## Exploring GaN Trench CAVET Performance from Cryogenic to Elevated Temperatures

*Xinyi Wen<sup>1</sup>, Allison Brand<sup>1</sup>, Junrui Lyu<sup>1</sup>, and Srabanti Chowdhury<sup>1</sup>* <sup>1</sup>Department of Electrical Engineering, Stanford University, Stanford, CA, USA [xinyiwen@stanford.edu](mailto:xinyiwen@stanford.edu)

### Introduction

Growing demand for compact and high-performance power electronics drives the pursuit of higher power density and efficiency. With its 3.4 eV bandgap, GaN supports high critical electric fields and elevated-temperature operation, while polarization effects in its heterostructures form a two-dimensional electron gas (2DEG) with high carrier density and mobility [1]. Among GaN vertical power transistors, the current-aperture vertical electron transistor (CAVET) uniquely integrates a vertical p-n junction for sustaining off-state voltages with a lateral 2DEG channel for low on-state channel resistance. Polarization-induced 2DEG formation is not subject to the freeze-out seen with impurity doping. These attributes make CAVETs well suited for extreme-temperature environments, where devices must remain functional under high-temperature degradation while offering enhanced performance at cryogenic conditions.

### Experimental Procedure

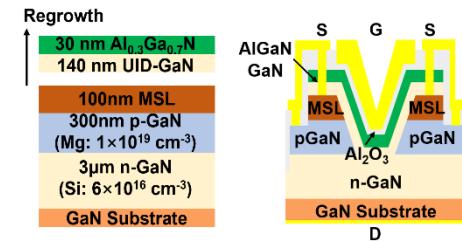

The trench CAVET (Fig. 1) was grown by an all-MOCVD process. The epitaxial p-n structure comprised a 3  $\mu$ m drift layer (Si:  $6 \times 10^{16} \text{ cm}^{-3}$ ) and a 300 nm p-GaN layer (Mg:  $1 \times 10^{19} \text{ cm}^{-3}$ ). A 100 nm GaN layer was grown at low temperature to prevent Mg out-diffusion [2]. The p-GaN was etched to form the aperture, followed by TMAH wet etching. After UV Ozone+HF surface treatments, MOCVD regrowth formed a 140 nm UID-GaN and a 30 nm Al<sub>0.3</sub>Ga<sub>0.7</sub>N layer. After isolation etching, the buried p-GaN was activated by RTA at 900 °C for 10 min. Ti/Al/Ni/Au source ohmic contact was deposited with post-annealing at 800 °C for 45 sec. Ni/Au p-GaN contact was deposited on the exposed p-GaN surface. A 15 nm ALD-Al<sub>2</sub>O<sub>3</sub> was deposited as the gate dielectric. A Ni/Au gate electrode was formed on top. A Ti/Au drain contact was deposited at the backside.

### Results and Discussion

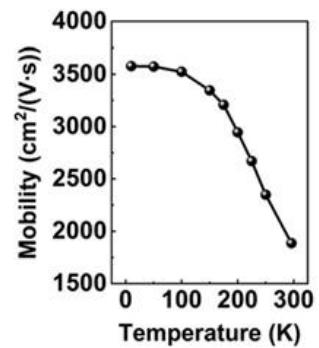

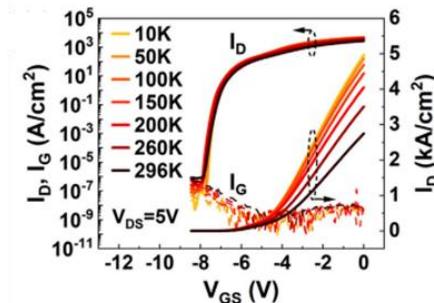

Electrical characterization at a range of temperatures from cryogenic (10 K) to room temperature (296 K), and after high temperature thermal shock testing serves as a preliminary assessment for GaN CAVETs in extreme temperature applications. Threshold voltage ( $V_{th}$ ) and 2DEG density remained stable throughout the 10 K to 296 K range.  $V_{th}$  had an average value of -7.45 V with standard deviation 0.069 V. 2DEG density was found with 1 MHz CV measurements to be  $7.36 \times 10^{12} \text{ cm}^{-2}$  at 296 K and  $6.83 \times 10^{12} \text{ cm}^{-2}$  at 10 K. Performance enhancements were observed over temperature reduction from 296 K to 10 K. Subthreshold slope (SS) decreased from 98.32 mV/dec to 51.31 mV/dec.  $I_{on}/I_{off}$  ratio increased from  $3 \times 10^9$  to  $9 \times 10^{10}$ . Peak field effect mobility increased from  $1886 \text{ cm}^2 / (\text{V}\cdot\text{s})$ , to  $3577 \text{ cm}^2 / (\text{V}\cdot\text{s})$ .  $R_{on,sp}$  reduced from  $1.02 \text{ m}\Omega\cdot\text{cm}^2$  to  $0.586 \text{ m}\Omega\cdot\text{cm}^2$ .

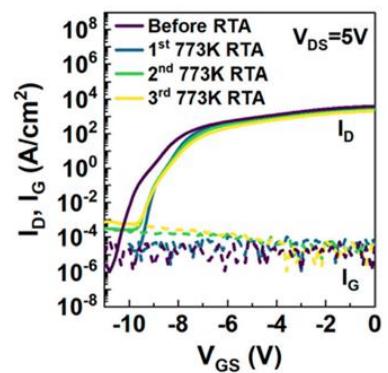

As an initial assessment of high temperature survivability, two trench CAVETs were subjected to RTA in a nitrogen ambient for one minute at 773 K and 1073 K, respectively. The device retained qualitative transistor behavior after three 773 K thermal shock tests, with performance reductions. Off-state gate leakage current increased gradually from  $10^{-5} \text{ A/cm}^2$  to  $10^{-3} \text{ A/cm}^2$ .  $R_{on,sp}$  increased sharply to  $1.58 \text{ m}\Omega\cdot\text{cm}^2$  after the first test, then remained mostly stable. One 1073 K test increased gate leakage to the point ( $\sim 10 \text{ A/cm}^2$ ) that the drain current could not be pinched off with gate control.  $R_{on,sp}$  jumped to  $24.2 \text{ m}\Omega\cdot\text{cm}^2$ , with an according reduction in output current. Visible metal degradation and peel-off were observed.

### Acknowledgements

This work is funded by KYOCERA Corporation, Japan.

### References

- [1] S. Chowdhury et al., IEEE TED, vol. 60, no. 10, pp. 3060-3066, 2013.

- [2] X. Wen, et al., Crystals, vol. 13, no. 4, p. 709, 2023.

Fig. 1: Schematic of GaN trench CAVET fabricated on a GaN substrate.

Fig. 2: Field effect mobility measured in lateral trench channel structure with identical epitaxial layers to CAVET.

Fig. 3:  $I_D$ - $V_{GS}$  transfer curve for trench CAVET from 296 K to 10 K.

Fig. 4:  $I_D$ - $V_{GS}$  transfer curve for trench CAVET after repeated thermal shock tests.