## Analysis of OFF-state Threshold Voltage Instability on Vertical GaN-on-Si Trench MOSFETs

M. Fregolent<sup>1,2</sup>, F. Bergamin<sup>1,2</sup>, D. Favero<sup>1,2</sup>, C. De Santi<sup>1,2</sup>, Andrea Cester<sup>1,2</sup>, C. Huber<sup>3</sup>, G. Meneghesso<sup>1,2</sup>, E. Zanoni<sup>1,2</sup>, and M. Meneghini<sup>1,2,4</sup>

<sup>1</sup> Department of Information Engineering, University of Padova, Padova, Italy

<sup>2</sup> IUNET - National Interuniversity Consortium for Nanoelectronics, Italy

<sup>3</sup> Department for Advanced Technologies and Micro Systems, Robert Bosch GmbH, Renningen, Germany

<sup>4</sup> Department of Physics and Astronomy, University of Padova, Padova, Italy

Corresponding Author email address: manuel.fregolent@unipd.it

### Introduction

GaN-based vertical devices on Silicon substrate are currently under study to provide a cost-effective alternative for Si- and SiC-based power devices targeting 1 kV and above. Despite the good performance of the devices, vertical devices are prone to several charge trapping processes involving deep levels in semiconductor and oxide layers [1], [2]. In this work, we will address the OFF-state induced threshold voltage instability in GaN trench MOSFETs.

### Experimental Procedures

The devices under test consist of GaN trench MOSFETs (TMOS) grown by MOCVD on a Silicon substrate. The epitaxial structure consists of a strain-relief buffer layer, an n<sup>+</sup>-GaN drain layer, n<sup>-</sup>-GaN drift layer, a p<sup>+</sup>-GaN body layer, and a n<sup>+</sup>-GaN source layer. The gate oxide layer (SiO<sub>2</sub>) was deposited by low-pressure chemical vapor deposition (LPCVD) at high temperature (880 °C) after the opening of the gate trench.

The threshold voltage instability of the devices was investigated by means of fast threshold voltage transients obtained with a custom experimental setup capable of applying arbitrary quiescent bias to the gate and drain terminals, that is periodically interrupted to perform an I<sub>D</sub>-V<sub>G</sub> measurement [1].

### Results and Discussion

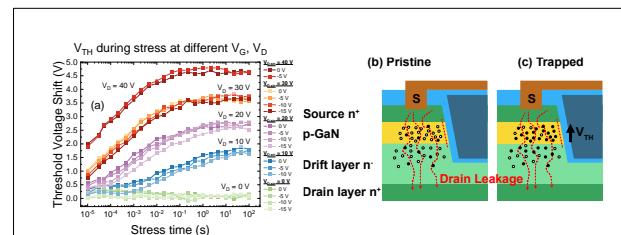

The experimental results, reported in **Figure 1(a)**, show that the devices present an increase of V<sub>TH</sub> when the devices are stressed in OFF-state condition even for limited bias (10 V – 40 V) with a “saturating logarithmic” kinetic. The experiment performed for several combinations of (V<sub>G</sub> ≤ 0 V, V<sub>D</sub>), shows that the negative gate voltage does not strongly affect the trapping mechanisms, thus suggesting the mechanism is due to the vertical epitaxial stack, rather than the gate module of the devices. The experiment repeated as function of temperature, revealed that the charge trapping process can be recovered only at high temperatures (> 200 °C) with an activation energy of approximately 1 eV. Capacitance deep level transient spectroscopy (C-DLTS) was performed on p-n diodes located on the same wafer, showing a good agreement of the main trap signature with respect to the one found during the V<sub>TH</sub> transient experiments.

The interpretation of the model is reported in **Figure 1(b,c)**: when the device is in OFF-state conditions, the drain leakage promoted by the threading dislocations transports electrons from the source towards the p-body layer. Here, the electrons are trapped in deep level defects and result in an increase of the V<sub>TH</sub> due to the negative charge [3].

### Acknowledgement

This project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 101007229. The JU receives support from the European Union's Horizon 2020 research & innovation program and Germany, France, Belgium, Austria, Sweden, Spain, Italy.

### References

- [1] M. Fregolent *et al.*, *Microelectronics Reliability*, vol. 150, p. 115130, Nov. 2023, doi: 10.1016/j.microrel.2023.115130.

- [2] Y. Ichikawa, *et al.*, *Applied Physics Express*, vol. 18, no. 3, p. 031002, Mar. 2025, doi: 10.35848/1882-0786/adbeb6.

- [3] M. Fregolent *et al.*, *Microelectronics Reliability*, vol. 169, Jun. 2025, doi: 10.1016/j.microrel.2025.115716.

**Figure 1:** (a) Threshold voltage instability detected during OFF-state experiments with different gate voltages; (b/c) Charge trapping model.