## Analysis of Turn-Off Instability Using Negative Gate Voltage

Kota Okada<sup>1</sup>, Sihoon Choi<sup>2</sup>, Kazuhiro Umetani<sup>1</sup>, Jun Imaoka<sup>2</sup>, Masayoshi Yamamoto<sup>2</sup>

Hironari Takase<sup>3</sup>, Juman Yoon<sup>3</sup>, Hiroki Nishi<sup>3</sup>

<sup>1</sup> Department of Electrical Engineering, Nagoya University,

<sup>2</sup> Institute of Materials Systems for Sustainability (IMass), Nagoya University

<sup>3</sup> Hyundai Mobility Japan R&D Center Co., Ltd.

Okada.kota.h7@s.mail.nagoya-u.ac.jp

### Introduction

Wide bandgap (WBG) semiconductor devices have garnered significant attention due to their superior performance in high-efficiency power conversion systems. However, their high-speed switching operations exacerbate the effects of parasitic inductances and capacitances inherent in circuit wiring and packaging. This can lead to undesirable phenomena such as false turn-on and self-sustained oscillation, which pose serious challenges in power conversion circuits. These issues not only increase switching losses and reduce system reliability, but can also cause permanent device failure, thereby threatening the stable and reliable operation of the entire system. This paper proposes a comprehensive instability analysis method for circuit turn-off conditions. Specifically, we conduct a combined analysis of false turn-on and damping ratio using small-signal equivalent circuits [1]. The objective is to precisely identify the operating regions where these instability phenomena occur.

### Proposed Method

#### a. False Turn-on Analysis

False turn-on is a phenomenon where rapid voltage or current changes feed back into the gate loop via the device's parasitic capacitances, causing the gate-source voltage to exceed the threshold voltage.

Our analysis method for this phenomenon proceeds as follows:

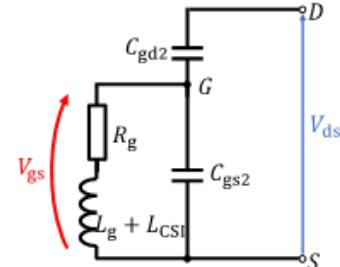

1. First, the drain-source voltage,  $V_{ds}(t)$ , generated across the device during turn-off is determined.

2. Next,  $V_{ds}(t)$  is treated as a voltage source, and the input-side impedance of the switching device is considered.

3. The gate-source voltage,  $V_{gs}(t)$ , is then calculated using the voltage division model shown in Fig. 1, which considers the impedance between the gate-source and gate-drain paths.

#### b. Turn-Off Instability Analysis

This study proposes an integrated analysis method for turn-off instability, combining false turn-on analysis with oscillation analysis based on damping ratio. The oscillation analysis is performed using a damping ratio analysis based on a small-signal equivalent circuit. Self-Sustained Oscillation is a phenomenon that occurs when false turn-on happens and the resulting ringing becomes unstable without decaying. Therefore, by integrating the results from these two analyses, the instability of the circuit operation can be evaluated.

Fig. 1. False turn-on analytical circuit

### Conclusion

In this paper, we proposed an integrated analysis method that evaluates the gate voltage and damping ratio during turn-off. This method showed the potential to evaluate the relationship between circuit instability during turn-off and the circuit's operating conditions.

### References

[1] Xue, P.; Maresca, L.; Riccio, M.; Breglio, G.; Irace, A. Self-Sustained Turn-Off Oscillation of SiC MOSFETs: Origin, Instability Analysis, and Prevention. *Energies* 2019, 12, 2211