# Unique techniques of ALD for semiconductor devices

Toshihide Nabatame

National Institute for Materials Science, 1-1 Namiki, Tsukuba, Ibaraki 305-0044, Japan.

Email: NABATAME.Toshihide@nims.go.jp / Phone: +81-29-860-4915

## 1. Introduction

Atomic layer deposition (ALD) technique is the optimal approach to fabricating conformal films on three-dimensional structures for semiconductor devices such as GaN and  $\text{Ga}_2\text{O}_3$  power devices, metal/high-k CMOS, oxide-semiconductor FET, DRAM, and FeRAM. ALD sequence generally consist of four steps: (a) Adsorption of precursor gas on the substrate, (b) Ar purge gas to exhaust residual precursor gas into chamber, (c) Reactant gas ( $\text{H}_2\text{O}$ ,  $\text{O}_3$ , O-plasma,  $\text{NH}_3$ , N-Plasma, etc.) to form target films (oxide, nitride, etc.) on substrate, (d) Ar purge gas to exhaust residual reactant gas into chamber. The four steps constitute one ALD cycle, and the growth rate is expressed as GPC. The GPC which depends on the precursor, ranges 0.03~0.2 nm/cycle. Until now, numerous studies have been conducted using the unique features of ALD. In this paper, I introduce several topics such as dipole control by ALD cycles for metal/high-k CMOS, selective adsorption of TDMAS precursor on  $\text{HfO}_2$  underlayer, and GaN surface modification by ALD-dummy- $\text{SiO}_2$  technique, mainly obtained in the author's group.

## 2. Dipole control by ALD cycle for metal/High-k CMOS

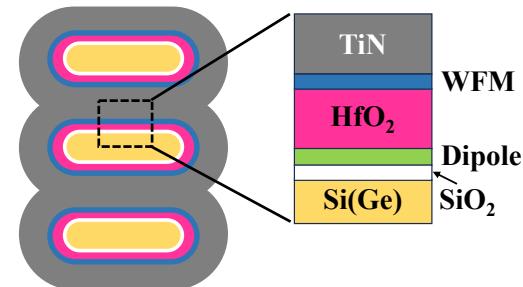

ALD became popular with the  $\text{HfO}_2$  film deposition as gate insulator of metal/high-k CMOS in around 2000 year. Metal/high-k CMOS is currently based on the GAA structure as shown in **Fig. 1**. To control  $V_{th}$ , the insertion of dipole layer between the  $\text{HfO}_2$  and  $\text{SiO}_2$  interfacial layer and WFM layer between the  $\text{HfO}_2$  and TiN gate electrode is being studied.  $\text{La}_2\text{O}_3$ ,  $\text{Y}_2\text{O}_3$ , and  $\text{Al}_2\text{O}_3$  have been mainly investigated as dipole layers for n- and p-MOSFETs, respectively [1,2]. It has been reported that  $V_{th}$  can be easily controlled by each ALD cycle. WFM was also fabricated using the ALD method by doping TiN with elements such as Al and O.

Fig. 1. Schematics of GAA (Gate-All-Around) structure with dipole and WFM layers.

## 3. Selective adsorption of TDMAS precursor on $\text{HfO}_2$ underlayer

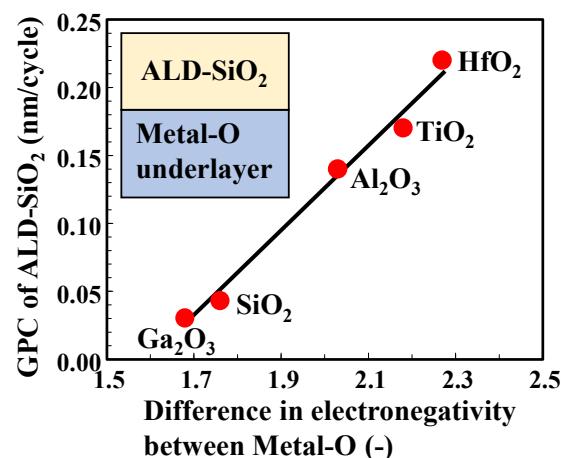

GaN MOS devices with amorphous  $\text{HfSiO}_x$ ,  $\text{AlSiO}_x$  and  $\text{HfAlO}_x$  gate insulators have been widely investigated as a means of obtaining superior device performance such as high  $g_m$  and low leakage current [3,4].  $\text{HfSiO}_x$  film was generally formed from the  $(\text{HfO}_2)_m/(\text{SiO}_2)_n$  laminate. Therefore, accurate GPC of the  $\text{SiO}_2$  layer deposited via ALD with TDMAS ( $\text{SiH}(\text{N}(\text{CH}_3)_2)_3$ ) precursor on the  $\text{HfO}_2$  layer was required. The GPC (0.22 nm/cycle) of ALD- $\text{SiO}_2$  film on  $\text{HfO}_2$  underlayer significantly increased compared to that on  $\text{SiO}_2$  underlayer (0.043 nm/cycle) [5]. To understand this behaviour, we studied the GPC of ALD- $\text{SiO}_2$  on various metal-oxide (M-O) underlayer. Surprisingly, the GPC of the ALD- $\text{SiO}_2$  film increased in the following order:  $\text{HfO}_2 > \text{TiO}_2 > \text{Al}_2\text{O}_3 > \text{SiO}_2 > \text{Ga}_2\text{O}_3$ . Furthermore, we found a correlation between the GPC of the ALD- $\text{SiO}_2$  film and the difference in the electronegativity of the M-O underlayer as shown in **Fig. 2**. Considering to ALD- $\text{SiO}_2$  growth mechanism, the Si atom which has a low positive charge, of the TDMAS precursor is selectively adsorbed toward the O atoms which has a high negative charge, of the M-O underlayer. As a results, a large amount of the TDMAS precursor adsorbed on  $\text{HfO}_2$  underlayer and led to high GPC. Based on these experimental data, we were able to fabricate the targeted Hf/Si ratio in the  $(\text{HfO}_2)_m/(\text{SiO}_2)_n$  laminate.

Fig. 2. Correlation between the GPC of the ALD- $\text{SiO}_2$  film and the difference in the electronegativity of M-O.

#### 4. GaN surface modification by ALD-dummy-SiO<sub>2</sub> technique

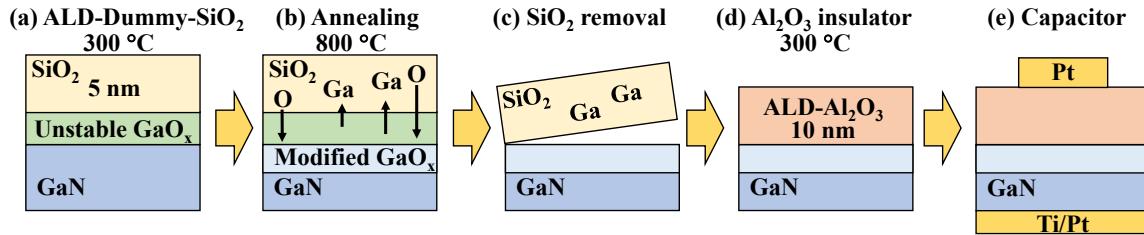

In GaN MOS capacitors, there is a native oxide (GaO<sub>x</sub>) film grown epitaxially on the GaN surface, which act as an electrically unstable GaO<sub>x</sub> layer [6]. To modify the unstable GaO<sub>x</sub> layer on GaN surface, we proposed ALD-dummy-SiO<sub>2</sub> technique, which is a unique and simple process as shown in **Fig. 3** [7,8]. ALD-dummy-SiO<sub>2</sub> layer (5 nm) was deposited on GaN and subsequently annealed at 800 °C in N<sub>2</sub>. The ALD-dummy-SiO<sub>2</sub>

Fig. 3. Schematics of GaN surface modification and capacitor fabrication by ALD-dummy-SiO<sub>2</sub> technique.

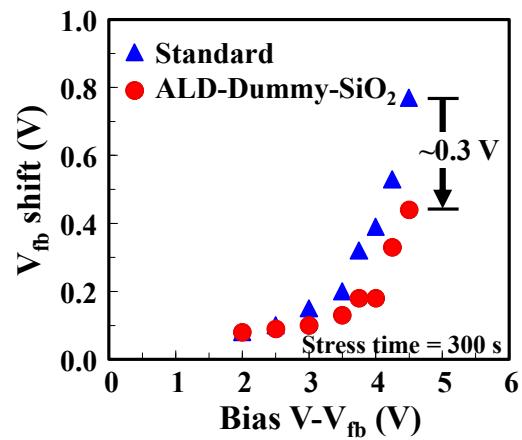

layer was removed with BHF solution. Next, a 10-nm-thick Al<sub>2</sub>O<sub>3</sub> insulator was deposited on the modified GaN substrate via ALD at 300 °C. Finally, Pt gate electrode and Ti/Pt ohmic contact were formed to fabricate n-GaN/Al<sub>2</sub>O<sub>3</sub>/Pt capacitor (ALD-dummy-SiO<sub>2</sub>). A n-GaN/Al<sub>2</sub>O<sub>3</sub>/Pt capacitor was also prepared without the ALD-dummy-SiO<sub>2</sub> process as reference (Standard). **Figure 4** shows the V<sub>fb</sub> shift as a function of bias V-V<sub>fb</sub> of the ALD-dummy-SiO<sub>2</sub> and Standard capacitors under positive bias stress. The V<sub>fb</sub> shift of the ALD-dummy-SiO<sub>2</sub> significantly reduced compared to that of the Standard. This is because the unstable GaO<sub>x</sub> layer was removed and oxygen-ordered GaO<sub>x</sub> layer was formed on the surface of GaN [9]. As a result, the modified GaN led to superior characteristics such as a small V<sub>fb</sub> shift under PBS.

I concluded that ALD is not the use as the equipment, but rather the utilization of its unique characteristics.

#### Acknowledgements

This work was supported by the MEXT Program for Creation of Innovative Core Technology for Power Electronics Grant Number JPJ009777 and ARIM(JPMXP1223NM5088).

#### References

- [1] K. Iwamoto et al., *Appl. Phys. Lett.* **92**, 132907 (2008).

- [2] H. Arimura et al., *Abst. of VLSI2025*, T19-3 (2025).

- [3] K. Ito et al., *J. Appl. Phys.* **129**, 084502 (2021).

- [4] T. Nabatame et al., *Appl. Phys. Express* **12**, 011009 (2019).

- [5] E. Maeda et al., *Jpn. J. Vac. Sci. Technol. A* **38**, 02409 (2020).

- [6] K. Yuge et al., *Semicond. Sci. Technol.* **34**, 034001 (2019).

- [7] Y. Irokawa et al., *ECS J. Solid. State Sci. Technol.* **13**, 085003 (2024).

- [8] M. Hara, *Mat. Sci. Semicond. Process.* **196**, 109606 (2025).

- [9] J. Uzuhashi et al., *ECS J. Solid. State Sci. Technol.* **14**, 085001 (2025).

Fig. 4. The V<sub>fb</sub> shift as a function of bias V-V<sub>fb</sub> of the ALD-dummy-SiO<sub>2</sub> and Standard capacitors under PBS.