Program IWDTF2025

## Thu. Nov 6, 2025

Poster Session | Electron device, process, and characterization

**★** Thu. Nov 6, 2025 5:00 PM - 6:30 PM JST | Thu. Nov 6, 2025 8:00 AM - 9:30 AM UTC **★** Exhibition Hall (BF1) **[PS] Poster Session**

[PS-01]

Depth profile analysis of charge trapping and chemical bonding states in Ni/SiO<sub>2</sub>/AlN/GaN structures by voltage-applied AR-HAXPES

\*Shunsuke Yamaguchi<sup>1</sup>, Yoshiharu Kirihara<sup>1</sup>, Yuichiro Mitani<sup>1</sup>, Mariko Shimizu<sup>2</sup>, Yukio Nakabayashi<sup>2</sup>, Yosuke Kajiwara<sup>2</sup>, Hiroshi Nohira<sup>1</sup> (1. Tokyo City University (Japan), 2. Toshiba Corporation, Corporate Laboratory (Japan))

[PS-02]

Anomalous Vg-Id Characteristics of GaN Power Device due to Ga penetration into AlN Interfacial Layers

\*Yusuke Katsuro<sup>1</sup>, Yoshiharu Kirihara<sup>1</sup>, Shunsuke Yamaguchi<sup>1</sup>, Makito Nishi<sup>1</sup>, Mariko Shimizu<sup>2</sup>, Yukio Nakabayashi<sup>2</sup>, Yousuke Kajiwara<sup>2</sup>, Hiroshi Nohira<sup>1</sup>, Yuichiro Mitani<sup>1</sup> (1. Tokyo City University (Japan), 2. Toshiba Corporation, Corporate Laboratory (Japan))

[PS-03]

Effect of Forming Gas Annealing for 3C-SiC n-MOSFET

Rima Nishizaki<sup>2</sup>, Dong Wang<sup>2</sup>, \*Keisuke Yamamoto<sup>2,1</sup> (1. Kumamoto University (Japan), 2. Kyushu University (Japan))

[PS-04]

IGZO Transistors with 700 °C Thermal Budget for Advanced DRAM Applications

\*Nannan You<sup>1,2</sup>, Tianhao Liao<sup>1,2</sup>, Jiayi Wang<sup>1,2</sup>, Yang Xu<sup>1,2</sup>, Shengkai Wang<sup>1,2</sup> (1. Institute of Microelectronics of Chinese Academy of Sciences (China), 2. Chinese Academy of Sciences (China))

[PS-05]

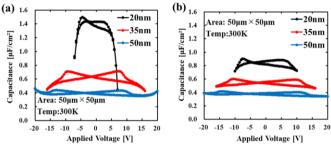

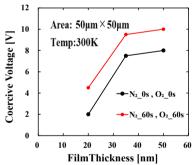

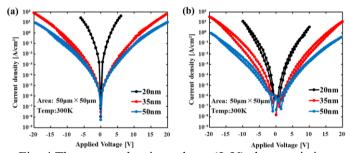

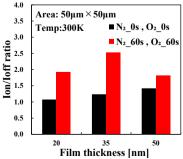

Influence of Ar/O<sub>2</sub> ratio during IGZO deposition on the electrical characteristics of a-IGZO metal-insulator-metal diodes

\*Chih An Chen<sup>1</sup>, Bai Jun Guo<sup>1</sup>, Chang Yi Yen<sup>1</sup>, Yu Hung Chen<sup>1</sup> (1. Department of Microelectronics Engineering, National Kaohsiung University of Science and Technology (NKUST) (Taiwan)) (Taiwan))

[PS-06]

Effect of annealing temperature on the electrical characteristics of Al/CuO/p-Si MOS capacitors

\*Siang-Yi Hong<sup>1</sup>, Xiao-Xuan Zeng<sup>1</sup>, Pei-Hsuan Su<sup>1</sup>, Yu-Hung Chen<sup>1</sup> (1. Department of Microelectronics Engineering, National Kaohsiung University of Science and Technology (NKUST) (Taiwan))

[PS-07]

Effects of Interface Formation Process on Tunneling Current Components of N-type Ti<sub>0.3</sub>Zn<sub>0.7</sub>O<sub>1.3</sub>/P-type Si Stack Structure

\*Kenta Ogawa<sup>1,2</sup>, Toyohiro Chikyow<sup>2</sup>, Atsushi Ogura<sup>1,3</sup>, Takahiro Nagata<sup>2,1</sup> (1. Meiji Univ. (Japan), 2. NIMS (Japan), 3. MREL (Japan))

[PS-08]

Classical Molecular Dynamics Simulation of Ferroelectric Properties of a-HfO<sub>2</sub>

\*Jumpei Ohba<sup>1</sup>, Sora Yamamoto<sup>1</sup>, Yusuke Nishimura<sup>1</sup>, Takunobu Watanabe<sup>1</sup> (1. Waseda University (Japan))

Program IWDTF2025

[PS-09]

# Effects of Al Concentration and Annealing Method on Crystalline and Ferroelectric properties of Al:HfO<sub>2</sub> Thin Films

\*Tomoya Mifune<sup>1</sup>, Hideaki Tanimura<sup>1,2</sup>, Yuma Ueno<sup>2</sup>, Yusuke Tani<sup>2</sup>, Yukiya Sano<sup>1</sup>, Hironori Fujisawa<sup>1</sup>, Seiji Nakashima<sup>1</sup>, Ai I Osaka<sup>1</sup>, Shinichi Kato<sup>2</sup>, Takumi Mikawa<sup>2</sup> (1. Univ. of Hyogo (Japan), 2. SCREEN (Japan))

[PS-10]

Consideration on the Coexisting Positive- and Negative-Imprinted Ferroelectric Domains and Their Imprint-Recovery in Non-Doped HfO<sub>2</sub> MFM Capacitor

\*Yukinori Morita<sup>1</sup>, Shutaro Asanuma<sup>1</sup>, Hiroyuki Ota<sup>1</sup>, Shinji Migita<sup>1</sup> (1. AIST (Japan))

[PS-11]

Polarization Inversion in Hf-based Oxide Layer with High Si Content in MOS Structure

\*Riku Kayagi<sup>1</sup>, Wataru Yasuda<sup>2</sup>, Akio Ohta<sup>3</sup>, Katsunori Makihara<sup>2</sup>, Yusuke Ichino<sup>1</sup>, Yoshiyuki Seike<sup>1</sup>, Tatsuo Mori<sup>1</sup>, Noriyuki Taoka<sup>1</sup> (1. Aichi Institute of Technology (Japan), 2. Nagoya University (Japan), 3. Fukuoka University (Japan))

[PS-12]

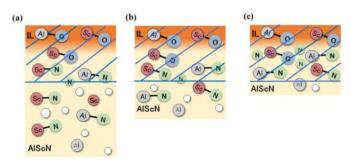

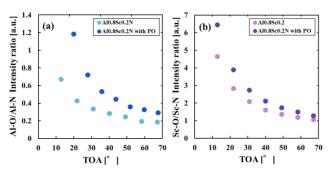

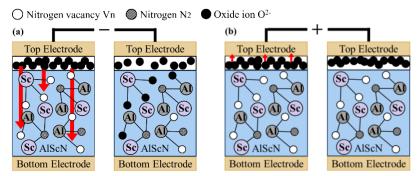

Effect of Plasma Treatment on Performance of AlScN-Based Ferroelectric Tunnel Junctions

\*Yuki Yamada<sup>1</sup>, Kazuki Goshima<sup>1</sup>, Yoshiharu Kirihara<sup>1</sup>, Ryouichi Kawai<sup>1</sup>, Kuniyuki Kakushima<sup>2</sup>, Hiroshi Nohira<sup>1</sup>, Yuichiro Mitani<sup>1</sup> (1. Tokyo City University (Japan), 2. Institute of Science Tokyo (Japan))

[PS-13]

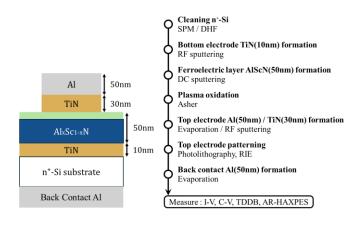

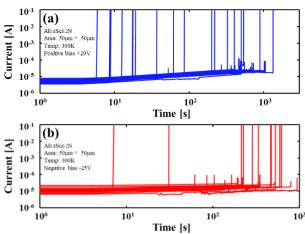

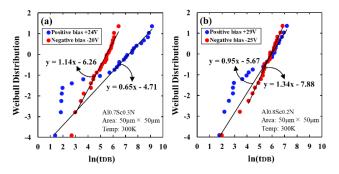

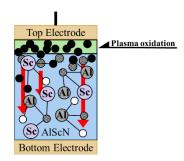

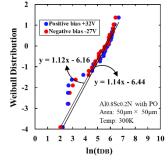

Study on Defect Generation in Ferroelectric AlScN from TDDB Statistical Point of View

\*Haruro Inoue<sup>1</sup>, Yuki Yamada<sup>1</sup>, Kazuki Goshima<sup>1</sup>, Yoshiharu Kirihara<sup>1</sup>, Kuniyuki Kakushima<sup>2</sup>, Hiroshi Nohira<sup>1</sup>, Yuichiro Mitani<sup>1</sup> (1. Tokyo City University (Japan), 2. Institute of Science Tokyo (Japan))

[PS-14]

Estimation of Charge Trap Positions in Silicon Nitride Films Using Voltage-applied Hard X-ray Photoelectron Spectroscopy

\*Yoshiharu Kirihara<sup>1</sup>, Hideyuki Yato<sup>1</sup>, Yuichiro Mitani<sup>1</sup>, Hiroshi Nohira<sup>1</sup> (1. Tokyo City University (Japan))

[PS-15]

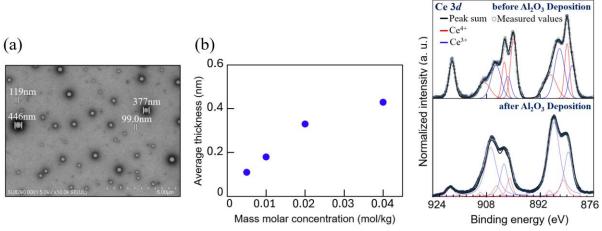

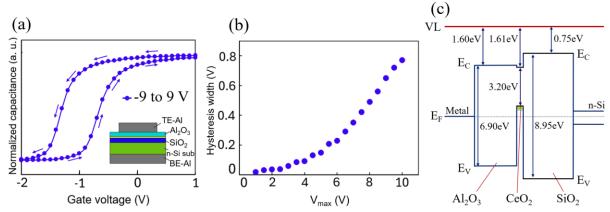

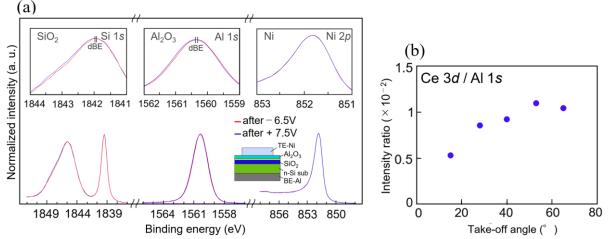

Fabrication of non-volatile memory using Al<sub>2</sub>O<sub>3</sub>/spin-coated CeO<sub>x</sub>/SiO<sub>2</sub>/Si stack

\*Hiroaki Tanaka<sup>1</sup>, Yoshiharu Kirihara<sup>1</sup>, Sorato Mikawa<sup>1</sup>, Tomoki Yoshida<sup>1</sup>, Ryousuke Ishikawa<sup>1</sup>, Hiroshi Nohira<sup>1</sup> (1. Tokyo City University (Japan))

[PS-16]

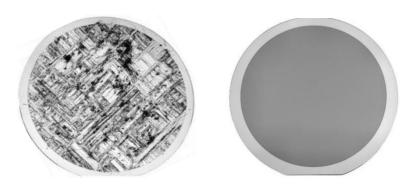

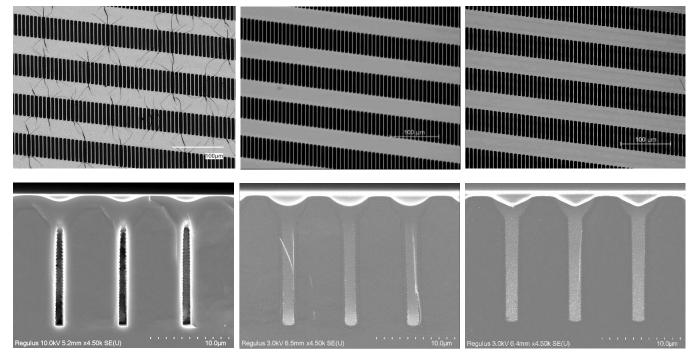

New SOD for Crack-Free Thick Film

\*Ikuya Ichie<sup>1</sup>, Kensuke Aida<sup>1</sup>, Kousuke Kabasawa<sup>1</sup>, Ryo Sasaki<sup>1</sup>, Naoko Nakamoto<sup>1</sup> (1. Merck Electronics Ltd. (Japan))

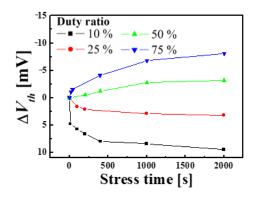

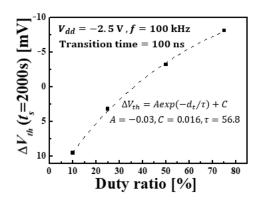

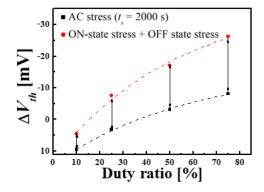

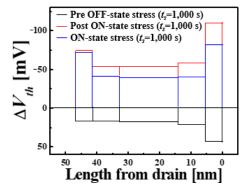

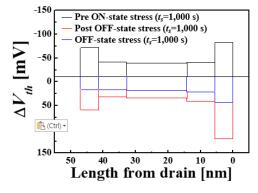

[PS-17]

Profile-Based Modeling of AC Stress-Induced Degradation in SiON pMOSFETs

\*Kyungmin Yoon<sup>1</sup>, Donghee Son<sup>2</sup>, Yeohyeok Yun<sup>1</sup> (1. Koreatech (Korea), 2. Samsung Electronics (Korea))

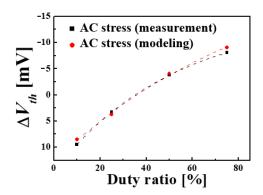

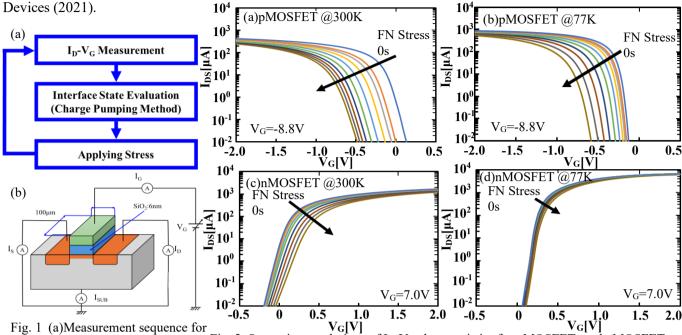

[PS-18]

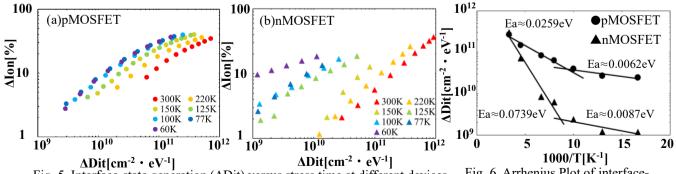

New Insights into MOS Interface Degradation of pMOSFETs and nMOSFETs at Cryogenic Temperature

\*Yuta Horiko<sup>1</sup>, Yutaro Masukawa<sup>1</sup>, Yuichiro Mitani<sup>1</sup> (1. Tokyo City University (Japan))

[PS-19]

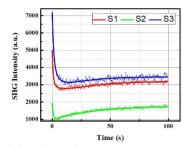

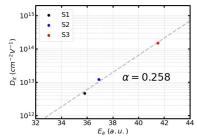

Nondestructive inspection of SiO2/Si interface defect density by nonlinear optics

\*Kuang Yao Lo<sup>1</sup>, Hua-Hsing Liu<sup>1</sup>, Ting-Yu Yen<sup>1</sup>, Chiu-Hsien Wu<sup>2</sup>, Kung-Ming Hung<sup>3</sup> (1. National Cheng Kung University (Taiwan), 2. National Chung Hsing University (Taiwan), 3. National Kaohsiung Univ. of Science and Technology (Taiwan))

Program IWDTF2025

[PS-20]

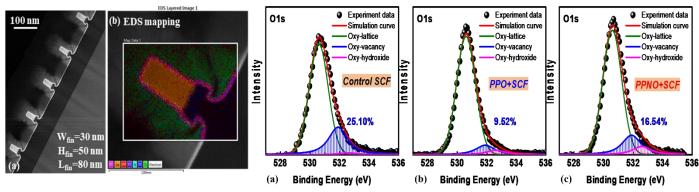

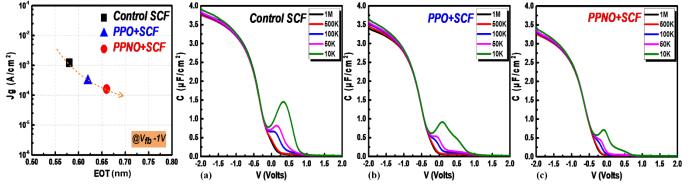

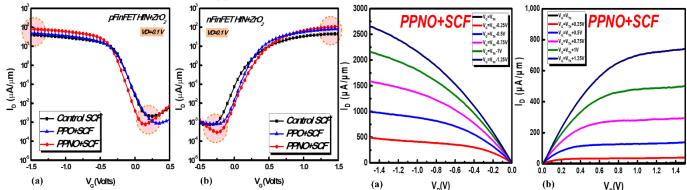

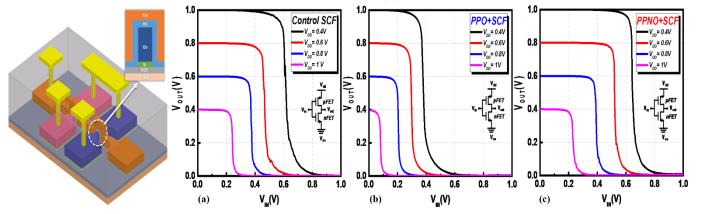

# High-Performance Ge FinFET CMOS Devices with Low-Temperature Supercritical Fluid Process after Post-Plasma Oxidation and Nitridation Treatments

\*Yu-Ren Lin<sup>1</sup>, Kuei-Shu Chang-Liao<sup>2</sup>, Kai-Chun Yang<sup>2</sup> (1. College of Semiconductor Research, National Tsing Hua University Hsinchu, Taiwan, R.O.C. (Taiwan), 2. Department of Engineering and System Science, National Tsing Hua University, Hsinchu 30013, Taiwan, R.O.C. (Taiwan))

[PS-21]

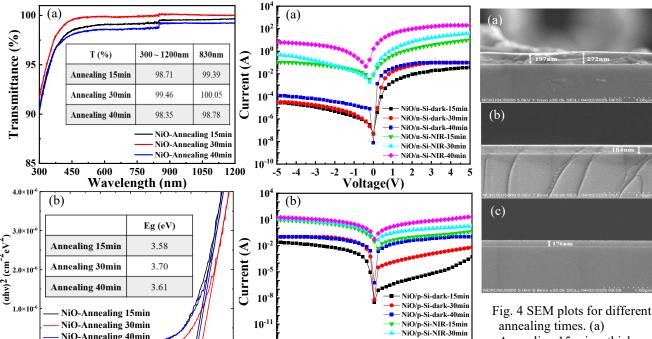

# Fabrication and Performance Analysis of Sol-Gel NiO/Si 830nm Near-Infrared Photodetectors Deposited by Spin-Coating Process

\*Yu Xin Feng<sup>1</sup>, Yu Hung Chen<sup>1</sup>, Chien Tso Lin<sup>1</sup>, Jia Hao Lin<sup>2</sup> (1. Department of Microelectronics Engineering, National Kaohsiung University of Science and Technology (NKUST) (Taiwan), 2. Opto-Electronics Technology Section Energy and Agile System Department, Metal Industries Research & Development Centre, Kaohsiung, (Taiwan))

[PS-22]

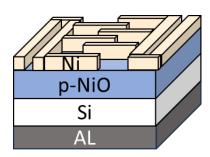

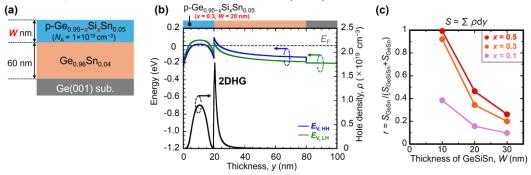

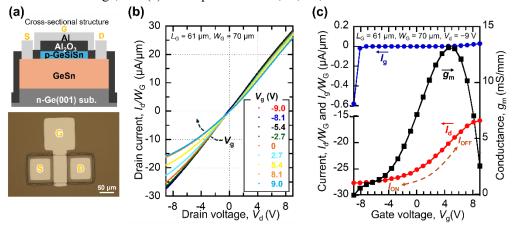

## New opportunity of GeSiSn/GeSn heterostructure for HEMT application

\*Shota Torimoto<sup>1</sup>, Mitsuo Sakashita<sup>1</sup>, Masashi Kurosawa<sup>1</sup>, Osamu Nakatsuka<sup>1,2</sup>, Shigehisa Shibayama<sup>1</sup> (1. Grad. Sch. of Eng., Nagoya Univ. (Japan), 2. IMaSS, Nagoya Univ. (Japan))

Session IWDTF2025

Poster Session | Electron device, process, and characterization

**★** Thu. Nov 6, 2025 5:00 PM - 6:30 PM JST | Thu. Nov 6, 2025 8:00 AM - 9:30 AM UTC **★** Exhibition Hall (BF1)

## [PS] Poster Session

[PS-01]

Depth profile analysis of charge trapping and chemical bonding states in Ni/SiO<sub>2</sub>/AlN/GaN structures by voltage-applied AR-HAXPES

\*Shunsuke Yamaguchi<sup>1</sup>, Yoshiharu Kirihara<sup>1</sup>, Yuichiro Mitani<sup>1</sup>, Mariko Shimizu<sup>2</sup>, Yukio Nakabayashi<sup>2</sup>, Yosuke Kajiwara<sup>2</sup>, Hiroshi Nohira<sup>1</sup> (1. Tokyo City University (Japan), 2. Toshiba Corporation, Corporate Laboratory (Japan))

[PS-02]

Anomalous Vg-Id Characteristics of GaN Power Device due to Ga penetration into AlN Interfacial Layers

\*Yusuke Katsuro<sup>1</sup>, Yoshiharu Kirihara<sup>1</sup>, Shunsuke Yamaguchi<sup>1</sup>, Makito Nishi<sup>1</sup>, Mariko Shimizu<sup>2</sup>, Yukio Nakabayashi<sup>2</sup>, Yousuke Kajiwara<sup>2</sup>, Hiroshi Nohira<sup>1</sup>, Yuichiro Mitani<sup>1</sup> (1. Tokyo City University (Japan), 2. Toshiba Corporation, Corporate Laboratory (Japan))

[PS-03]

Effect of Forming Gas Annealing for 3C-SiC n-MOSFET

Rima Nishizaki<sup>2</sup>, Dong Wang<sup>2</sup>, \*Keisuke Yamamoto<sup>2,1</sup> (1. Kumamoto University (Japan), 2. Kyushu University (Japan))

[PS-04]

IGZO Transistors with 700 °C Thermal Budget for Advanced DRAM Applications

\*Nannan You<sup>1,2</sup>, Tianhao Liao<sup>1,2</sup>, Jiayi Wang<sup>1,2</sup>, Yang Xu<sup>1,2</sup>, Shengkai Wang<sup>1,2</sup> (1. Institute of Microelectronics of Chinese Academy of Sciences (China), 2. Chinese Academy of Sciences (China))

[PS-05]

Influence of Ar/O<sub>2</sub> ratio during IGZO deposition on the electrical characteristics of a-IGZO metal-insulator-metal diodes

\*Chih An Chen<sup>1</sup>, Bai Jun Guo<sup>1</sup>, Chang Yi Yen<sup>1</sup>, Yu Hung Chen<sup>1</sup> (1. Department of Microelectronics Engineering, National Kaohsiung University of Science and Technology (NKUST) (Taiwan)) (Taiwan))

[PS-06]

Effect of annealing temperature on the electrical characteristics of Al/CuO/p-Si MOS capacitors

\*Siang-Yi Hong<sup>1</sup>, Xiao-Xuan Zeng<sup>1</sup>, Pei-Hsuan Su<sup>1</sup>, Yu-Hung Chen<sup>1</sup> (1. Department of Microelectronics Engineering, National Kaohsiung University of Science and Technology (NKUST) (Taiwan))

[PS-07]

Effects of Interface Formation Process on Tunneling Current Components of N-type  $Ti_{0.3}Zn_{0.7}O_{1.3}/P$ -type Si Stack Structure

\*Kenta Ogawa<sup>1,2</sup>, Toyohiro Chikyow<sup>2</sup>, Atsushi Ogura<sup>1,3</sup>, Takahiro Nagata<sup>2,1</sup> (1. Meiji Univ. (Japan), 2. NIMS (Japan), 3. MREL (Japan))

[PS-08]

Classical Molecular Dynamics Simulation of Ferroelectric Properties of a-HfO<sub>2</sub>

Session IWDTF2025

\*Jumpei Ohba<sup>1</sup>, Sora Yamamoto<sup>1</sup>, Yusuke Nishimura<sup>1</sup>, Takunobu Watanabe<sup>1</sup> (1. Waseda University (Japan))

[PS-09]

Effects of Al Concentration and Annealing Method on Crystalline and Ferroelectric properties of Al:HfO<sub>2</sub> Thin Films

\*Tomoya Mifune<sup>1</sup>, Hideaki Tanimura<sup>1,2</sup>, Yuma Ueno<sup>2</sup>, Yusuke Tani<sup>2</sup>, Yukiya Sano<sup>1</sup>, Hironori Fujisawa<sup>1</sup>, Seiji Nakashima<sup>1</sup>, Ai I Osaka<sup>1</sup>, Shinichi Kato<sup>2</sup>, Takumi Mikawa<sup>2</sup> (1. Univ. of Hyogo (Japan), 2. SCREEN (Japan))

[PS-10]

Consideration on the Coexisting Positive- and Negative-Imprinted Ferroelectric Domains and Their Imprint-Recovery in Non-Doped HfO<sub>2</sub> MFM Capacitor

\*Yukinori Morita<sup>1</sup>, Shutaro Asanuma<sup>1</sup>, Hiroyuki Ota<sup>1</sup>, Shinji Migita<sup>1</sup> (1. AIST (Japan))

[PS-11]

Polarization Inversion in Hf-based Oxide Layer with High Si Content in MOS Structure \*Riku Kayagi¹, Wataru Yasuda², Akio Ohta³, Katsunori Makihara², Yusuke Ichino¹, Yoshiyuki Seike¹, Tatsuo Mori¹, Noriyuki Taoka¹ (1. Aichi Institute of Technology (Japan), 2. Nagoya University (Japan), 3. Fukuoka University (Japan))

[PS-12]

Effect of Plasma Treatment on Performance of AlScN-Based Ferroelectric Tunnel Junctions \*Yuki Yamada<sup>1</sup>, Kazuki Goshima<sup>1</sup>, Yoshiharu Kirihara<sup>1</sup>, Ryouichi Kawai<sup>1</sup>, Kuniyuki Kakushima<sup>2</sup>, Hiroshi Nohira<sup>1</sup>, Yuichiro Mitani<sup>1</sup> (1. Tokyo City University (Japan), 2. Institute of Science Tokyo (Japan))

[PS-13]

Study on Defect Generation in Ferroelectric AlScN from TDDB Statistical Point of View \*Haruro Inoue<sup>1</sup>, Yuki Yamada<sup>1</sup>, Kazuki Goshima<sup>1</sup>, Yoshiharu Kirihara<sup>1</sup>, Kuniyuki Kakushima<sup>2</sup>, Hiroshi Nohira<sup>1</sup>, Yuichiro Mitani<sup>1</sup> (1. Tokyo City University (Japan), 2. Institute of Science Tokyo (Japan))

[PS-14]

Estimation of Charge Trap Positions in Silicon Nitride Films Using Voltage-applied Hard X-ray Photoelectron Spectroscopy

\*Yoshiharu Kirihara<sup>1</sup>, Hideyuki Yato<sup>1</sup>, Yuichiro Mitani<sup>1</sup>, Hiroshi Nohira<sup>1</sup> (1. Tokyo City University (Japan))

[PS-15]

Fabrication of non-volatile memory using Al<sub>2</sub>O<sub>3</sub>/spin-coated CeO<sub>x</sub>/SiO<sub>2</sub>/Si stack

\*Hiroaki Tanaka<sup>1</sup>, Yoshiharu Kirihara<sup>1</sup>, Sorato Mikawa<sup>1</sup>, Tomoki Yoshida<sup>1</sup>, Ryousuke Ishikawa<sup>1</sup>, Hiroshi Nohira<sup>1</sup> (1. Tokyo City University (Japan))

[PS-16]

New SOD for Crack-Free Thick Film

\*Ikuya Ichie<sup>1</sup>, Kensuke Aida<sup>1</sup>, Kousuke Kabasawa<sup>1</sup>, Ryo Sasaki<sup>1</sup>, Naoko Nakamoto<sup>1</sup> (1. Merck Electronics Ltd. (Japan))

[PS-17]

Profile-Based Modeling of AC Stress-Induced Degradation in SiON pMOSFETs

\*Kyungmin Yoon<sup>1</sup>, Donghee Son<sup>2</sup>, Yeohyeok Yun<sup>1</sup> (1. Koreatech (Korea), 2. Samsung Electronics (Korea))

[PS-18]

©IWDTF

Session IWDTF2025

New Insights into MOS Interface Degradation of pMOSFETs and nMOSFETs at Cryogenic Temperature

\*Yuta Horiko<sup>1</sup>, Yutaro Masukawa<sup>1</sup>, Yuichiro Mitani<sup>1</sup> (1. Tokyo City University (Japan))

[PS-19]

Nondestructive inspection of SiO2/Si interface defect density by nonlinear optics

\*Kuang Yao Lo<sup>1</sup>, Hua-Hsing Liu<sup>1</sup>, Ting-Yu Yen<sup>1</sup>, Chiu-Hsien Wu<sup>2</sup>, Kung-Ming Hung<sup>3</sup> (1. National Cheng Kung University (Taiwan), 2. National Chung Hsing University (Taiwan), 3. National Kaohsiung Univ. of Science and Technology (Taiwan))

[PS-20]

High-Performance Ge FinFET CMOS Devices with Low-Temperature Supercritical Fluid Process after Post-Plasma Oxidation and Nitridation Treatments

\*Yu-Ren Lin<sup>1</sup>, Kuei-Shu Chang-Liao<sup>2</sup>, Kai-Chun Yang<sup>2</sup> (1. College of Semiconductor Research, National Tsing Hua University Hsinchu, Taiwan, R.O.C. (Taiwan), 2. Department of Engineering and System Science, National Tsing Hua University, Hsinchu 30013, Taiwan, R.O.C. (Taiwan))

[PS-21]

Fabrication and Performance Analysis of Sol-Gel NiO/Si 830nm Near-Infrared Photodetectors Deposited by Spin-Coating Process

\*Yu Xin Feng<sup>1</sup>, Yu Hung Chen<sup>1</sup>, Chien Tso Lin<sup>1</sup>, Jia Hao Lin<sup>2</sup> (1. Department of Microelectronics Engineering, National Kaohsiung University of Science and Technology (NKUST) (Taiwan), 2. Opto-Electronics Technology Section Energy and Agile System Department, Metal Industries Research & Development Centre, Kaohsiung, (Taiwan))

[PS-22]

New opportunity of GeSiSn/GeSn heterostructure for HEMT application \*Shota Torimoto<sup>1</sup>, Mitsuo Sakashita<sup>1</sup>, Masashi Kurosawa<sup>1</sup>, Osamu Nakatsuka<sup>1,2</sup>, Shigehisa

Shibayama<sup>1</sup> (1. Grad. Sch. of Eng., Nagoya Univ. (Japan), 2. IMaSS, Nagoya Univ. (Japan))

PS-01 IWDTF2025

# Depth profile analysis of charge trapping and chemical bonding states in Ni/SiO<sub>2</sub>/AlN/GaN structures by voltage-applied AR-HAXPES

Shunsuke Yamaguchi<sup>1</sup>, Yoshiharu Kirihara<sup>1</sup>, Yuichiro Mitani<sup>1</sup>, Mariko Shimizu<sup>2</sup>, Yukio Nakabayashi<sup>2</sup>, Yosuke Kajiwara<sup>2</sup>, and Hiroshi Nohira<sup>1</sup>

<sup>1</sup>Tokyo city Univ., <sup>2</sup>Toshiba Corporation, Corporate Laboratory <sup>1</sup>1-28-1 Tamazutsumi, Setagaya-ku, Tokyo 158-8557, Japan Email: g2581296@tcu.ac.jp/Phone +81-3-5707-0104

#### 1. Introduction

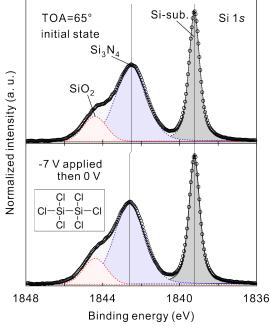

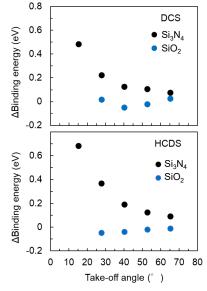

In recent years, high-efficiency power conversion has been required in fields such as telecommunication base stations and data centers. To achieve this, it is expected that power devices using gallium nitride (GaN), a next-generation power device material, will offer higher performance [1]. In particular, GaN power devices with trench structures are expected to achieve both high integration and low loss. However, a major challenge is to solve reliability issues such as threshold change, which is believed to be caused by charge trapping in the dielectric film. To solve this problem, we have investigated the distribution and origin of the traps in the dielectric film by using voltage-applied angle-resolved hard X-ray photoelectron spectroscopy (AR-HAXPES), based on the changes in the photoelectron spectra before and after the application of voltage stress.

#### 2. Experimental Procedure

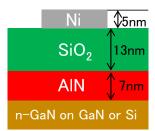

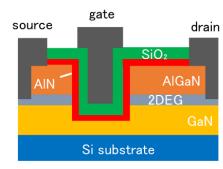

Figure 1 shows the structure of the measured samples. These samples were measured using voltage-applied AR-HAXPES measurements at BL09XU [2] (hv = 7933 eV) at SPring-8 with take-off angles (hereafter TOA) ranging from 12.7° to 67.3°. Photoelectrons from the inner shells of Al 1s, Si 1s, Ga 2p, N 1s and O 1s were measured. Here, the Ni electrode was grounded and voltage was applied to the GaN substrate. In the figures and tables, the voltage is indicated by the potential of the Ni electrode with respect to the GaN, so the polarity is opposite to the actual applied voltage.

#### 3. Results and Discussion

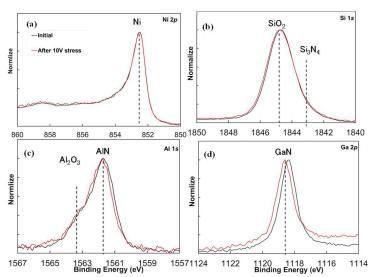

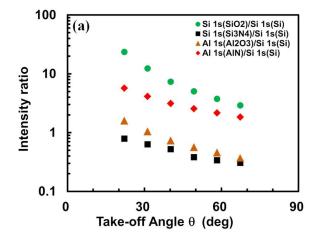

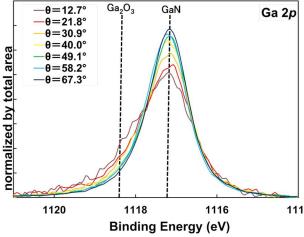

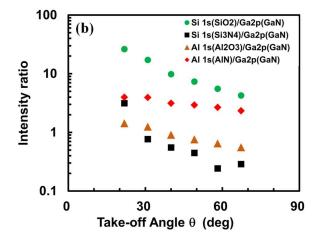

Figures 2(a), (b), (c), and (d) show the photoelectron spectra of Ni 2p, Si 1s, Al 1s, and Ga 2p measured before and after applying 10 V voltage stress, respectively. Note that no voltage is applied during either measurement. Figures 2(b) and 2(c) show that the reaction occurred at the interface between SiO<sub>2</sub> and AlN, forming Si-N and Al-O. The binding energy of Ga 2p increases after voltage stress as shown in Fig. 2(d). This suggests that holes are trapped or electrons are de-trapped in the SiO<sub>2</sub>/AlN layer due to voltage stress. The fact that the Ni 2p shift is not observed indicates that it is not a charge-up. The differences in the binding energies of photoelectrons from their respective inner-shell orbitals before and after the application of voltage stress are shown in Table 1. The large shift in Ga 2p and Al 1s means that charge trapping occurs in the AlN film and at the SiO<sub>2</sub>/AlN interface. Table 2 shows the shift of binding energy from their initial binding energy when the applied voltage is 5 V, 7 V, and 10 V. Table 2 shows that the higher the applied voltage, the larger the binding energy shift. Figure 3 shows Ga 2p photoelectron spectra measured at various angles, normalized by total photoelectron intensity. The figure shows that the percentage of intensity from oxidized Ga increases as TOA decreases. This suggests that a part of Ga diffuses to the vicinity of the SiO<sub>2</sub>/AlN interface. Figure 4 shows the TOA dependence of the intensity ratios of other photoelectron spectra on the Si 1s photoelectron intensity from the Si substrate (a) and the Ga 2p photoelectron intensity from the GaN substrate (b). From the figure, it can be seen that the angular dependence of Al 1s/Ga 2p on the GaN substrate is smaller than that on the Si substrate. This indicates that Ga diffuses into the AlN film, which is also consistent with the result in Figure 3. From the above, the origin of the charge trap is likely to be Ga diffused in AlN.

#### Acknowledgement

The synchrotron radiation experiments were performed at BL09XU of SPring-8 with the approval of Japan Synchrotron Radiation Research Institute (JASRI, Proposal Nos.2024B1695, 2025A1643, 2025A1574, 2025A1803, and 2025A1824).

#### References

[1] T. Avraham et al., Energies 18, 1046 (2025). [2] A. Yasui et al., J. Synchrotron Radiat. 30, 1013 (2023).

© IWDTF2025 - PS-01 -

PS-01 IWDTF2025

Fig. 1 Schematic structure of samples.

Fig. 2 (a) Ni 2p, (b) Si 1s, (c) Al 1s, and (d) Ga 2p photoelectron spectra measured by HAXPES, respectively.

Table 1 Binding energies of Si 1s, Al 1s and Ga 2p photoelectrons before and after applying voltage stress and the amount of change ( $\Delta$ V) after applying stress.

| Sample condition | Binding Energy (eV)      |            |            |

|------------------|--------------------------|------------|------------|

| Sample condition | Si 1s(SiO <sub>2</sub> ) | Al 1s(AlN) | Ga 2p(GaN) |

| Initial          | 1844.735                 | 1561.664   | 1118.402   |

| After 10V stress | 1844.763                 | 1561.790   | 1118.627   |

| $(\Delta V)$     | (0.028)                  | (0.126)    | (0.225)    |

Table 2 Stress voltage dependence of the change in binding energy of Si 1s,Al 1s and Ga 2p photoelectrons.

| Sample condition | Amount of change ΔV (eV) |            |            |

|------------------|--------------------------|------------|------------|

| Sample condition | Si 1s(SiO <sub>2</sub> ) | Al 1s(AlN) | Ga 2p(GaN) |

| After-5V stress  | 0.018                    | 0.073      | 0.164      |

| After 7V stress  | 0.019                    | 0.119      | 0.189      |

| After10V stress  | 0.028                    | 0.126      | 0.225      |

Fig. 3 TOA dependence of Ga 2p photoelectron spectra. Here, the height is normalized by the total spectral area.

Fig. 4 TOA dependence of the photoelectron spectral intensity ratio normalized by the photoelectron intensity from the substrate. Here, (a) is for Si substrate and (b) is for GaN substrate.

PS-02 IWDTF2025

# Anomalous Vg-Id Characteristics of GaN Power Device due to Ga penetration into AlN Interfacial Layers

Yusuke Katsuro<sup>1</sup>, Shunsuke Yamaguchi<sup>1</sup>, Yoshiharu Kirihara<sup>1</sup>, Makito Nishi<sup>1</sup>, Mariko Shimizu<sup>2</sup>, Yukio Nakabayashi<sup>2</sup>, Yousuke Kajiwara<sup>2</sup>, Hiroshi Nohira<sup>1</sup>, and Yuichiro Mitani<sup>1</sup>

Tokyo City Univ., <sup>2</sup>Toshiba Corporation, Corporate Laboratory

1-28-1 Tamazutsumi, Setagaya-ku, Tokyo 158-8557, Japan

Email: g2481225@tcu.ac.ip / Phone: +81-3-5707-0104

#### 1. Introduction

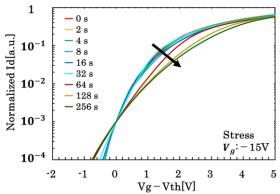

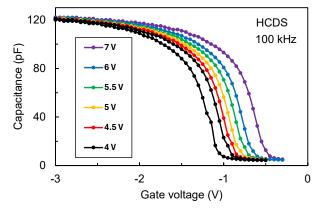

GaN MOSFETs are promising power devices due to their high breakdown voltage and fast switching speed. In recent, introducing an AlN interfacial layer (IL) between the gate insulator and GaN channel has been reported to enhance mobility and suppress Vth variation by suppressing Ga penetration [1][2]. However, the device exhibited anomalous subthreshold swing (SS) degradation under negative bias stress as shown in Fig.1. It is also imperative to ensure the stability of the threshold voltage (Vth) to guarantee reliable operation. Therefore, in this study, we investigate the physical origin of this anomalous SS behaviour.

## 2. Experimental Procedure

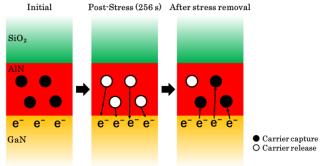

A schematic cross-sectional view of the device structure is shown in Fig. 2. The channel width (W) and length (L) of the device used in this study are 20  $\mu$ m and 1  $\mu$ m, respectively, with an AlN interfacial layer of 3 nm.

#### 3. Results and Discussion

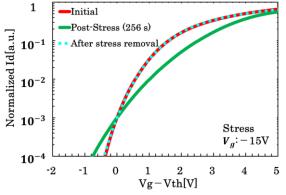

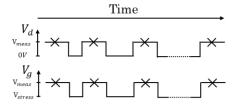

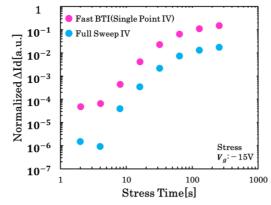

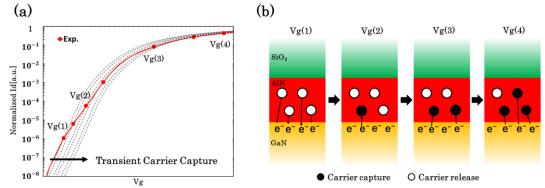

Fig. 3 shows the Id-(Vg-Vth) characteristics of the device under three conditions: initial (before stress), post-stressed (after applying Vg = -15 V for 256 s), and after stress removal, where the Id-Vg curve was remeasured without applying stress. After the stress, the Id-Vg curve shows an anomalous degradation of the subthreshold swing (SS). On the contrary, after the gate voltage are turned off the Id-Vg characteristics are recovered immediately, the SS almost coincides with that observed in the initial Id-Vg curve. This result indicates the contribution of the carrier trapping / detrapping defects as schematically shown in Fig. 4. Under negative gate bias stress, the carriers captured in defect energy levels within the AlN layer are released, resulting in a negative shift in Vth. Subsequently, during the recovery phase, the carriers are re-trapped, which results in the recovery of the Id-Vg curve. According to the HAXPES measurement, it is inferred that the defects are attributable to the penetration of Ga into the AlN layer [4]. That is, the existence of these carrier trapping detrapping in the AlN layer may be related to the anomalous Id-Vg characteristics observed after stress as shown in Fig. 1. To verify this hypothesis, we performed the single-point fast BTI measurements while minimizing recovery during the measurement. The measurement sequence of the fast BTI method is shown in Fig. 5. Fig. 6 shows the comparison between the  $\Delta Id$  by using the fast BTI measurement and that by using the full-sweep IV measurement. By the full-sweep IV method,  $\Delta Id$  values are smaller compared to those by the fast BTI method. This result indicates that the recovery during the full-sweep IV measurement caused by fast carrier trapping / detrapping occurs. Based on these results, it is inferred that the transient carrier trapping during the Vg sweep causes the anomalous SS degradation [5]. Fig. 7 presents schematic diagrams for the anomalous SS degradation due to transient carrier trapping during full-sweep IV measurement. When negative bias stress is applied, electrons are emitted and Vth shifts in the negative direction, but during the Vg sweep, transient electron re-trapping occurs, which leads to apparent SS degradation.

#### 4. Conclusions

This study investigated the origin of anomalous SS degradation observed in GaN MOSFETs with an AlN interlayer under negative bias stress. Full-sweep IV measurements showed significant SS degradation, but Fast BTI revealed that it was caused by transient carrier trapping during measurement. The observed recovery behaviour also suggests fast trap/detrap dynamics in the AlN layer. These findings highlight the need to consider measurement-induced effects for the accurate reliability measurement of GaN MOSFETs.

#### References

[1] Y. Kajiwara et al., ISPSD. 32, 302 (2020).[2] K. Ito et al., IEDM. (2023).[3] X. Garros et al., IEEE IRPS, 2018.[4] S. Yamaguchi et al., to be presented in IWDTF-2025. [5] Y. Miyaki et al., IEEE IMFEDK, 2024.

© IWDTF2025 - PS-02 -

PS-02 IWDTF2025

Fig.1. Stress time evolutions of Id-Vg characteristics of GaN MOSFETs measured at Vd = 1 V. Negative gate stress of Vg = -15 V are applied.

Fig.3. Comparing Id-Vg characteristics prior to stress and following negative bias stress (Vg = -15 V) for 256 sec, and recovered after stress removal.

Fig.5. Measurement sequence of Fast BTI method using single-point Id measurement.

Fig. 2. Schematic cross-sectional image of GaN-MOSFETs (W/L = 20/1 µm), where 2DEG denotes a two-dimensional electron gas.

Fig.4. Schematic diagram of physical model for initial, post-stressed, and recovered Id-Vg characteristics.

Fig.6.  $\Delta$  Id as a function of stress time obtained by full sweep IV comparing to that by Fast BTI measurement.

Fig.7. (a) Positive shift of Id-Vg characteristics due to electron trapping to generated bulk traps (*i.e.* transient carrier capture). When electron trapping increases transiently as increasing Vg, Id-Vg curve gradually shifts to the positive direction, where the dashed lines schematically illustrate Id–Vg curves without trapping at each point. (b) Schematic diagram of physical model explaining the mechanism of transient carrier trapping and its impact on the observed degradation behavior in SS.

PS-03 IWDTF2025

## Effect of Forming Gas Annealing for 3C-SiC n-MOSFET

Rima Nishizaki<sup>1</sup>, Dong Wang<sup>2</sup>, and Keisuke Yamamoto<sup>2,3</sup>

<sup>1</sup>Interdisciplinary Graduate School of Engineering Sciences, Kyushu University

<sup>2</sup>Faculty of Engineering Sciences, Kyushu University

6-1, Kasuga-koen, Kasuga, Fukuoka 816-8580, Japan

<sup>3</sup>Research and Education Institute for Semiconductors and Informatics, Kumamoto University

2-39-1, Kurokami, Chuo-ku, Kumamoto, 860-8555, Japan

Email: yamamoto.keisuke.380@cs.kumamoto-u.ac.jp / Phone: +81-96-342-3591

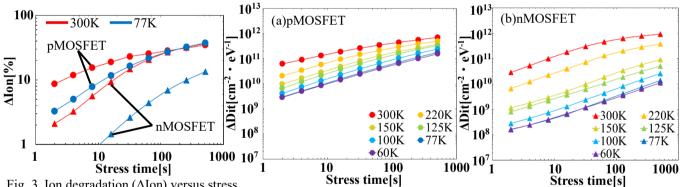

#### 1. Introduction

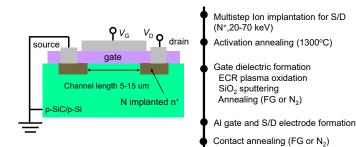

Silicon carbide (SiC) has a high breakdown electric field and a wide bandgap, which are advantages for realizing high-efficiency power devices and devices that can operate at high temperatures. Among the polytypes of SiC, high-quality (111)-oriented cubic SiC (3C-SiC) can be grown epitaxially on Si (111) substrates [1]. For the application of 3C-SiC to electronic devices, the formation of an insulating film with excellent interfacial properties is essential for both MOS gate dielectrics and surface passivation layers. We have previously reported that sputter-deposited SiO<sub>2</sub> combined with a plasma-oxidized interfacial layer (IL) provides high interfacial quality on 3C-SiC, and MOSFETs employing this gate stack exhibit a high field-effect mobility ( $\mu_{FE}$ ) of 131 cm<sup>2</sup>/Vs [2,3]. In this study, we introduce forming gas annealing (FGA) into the gate stack process [4]. As a result, improvements in device performance, particularly  $\mu_{FE}$ , were obtained for 3C-SiC MOSFETs.

#### 2. Experimental Procedure

The substrate was (111)-oriented, boron-doped p-type 3C-SiC epitaxially grown on a p-Si (111) wafer, with a hole concentration on the order of 10<sup>15</sup> cm<sup>-3</sup>. The fabrication procedure is outlined in Fig. 1. All MOSFETs were designed with a current flow direction of <110>. Source/drain (S/D) regions were formed through a multistep nitrogen ion implantation process (20–70 keV) using a patterned SiO<sub>2</sub> mask at 500 °C, followed by activation annealing at 1300 °C. The gate stack was subsequently formed by introducing an electron cyclotron resonance (ECR) plasma-oxidized IL and sputter-deposited SiO<sub>2</sub> (30 nm). Post-deposition annealing (PDA) was conducted in forming gas (FG, Ar:H<sub>2</sub> = 9:1) at 400 °C for 30 min. Thermally evaporated Al was used as the gate and S/D electrodes, followed by contact annealing (CA) in FG at 300 °C. For comparison, MOSFETs treated N<sub>2</sub> PDA and CA instead of FG annealing were also prepared.

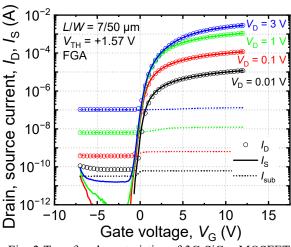

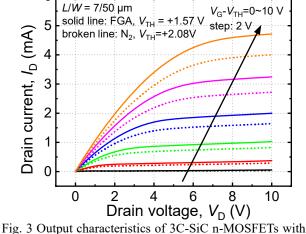

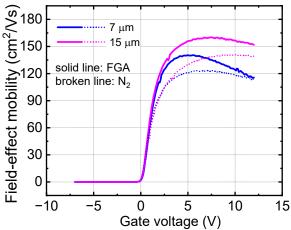

#### 3. Results and Discussion

Figure 2 shows the transfer characteristics (drain current  $I_D$ , source current  $I_S$  vs gate voltage  $V_G$ ) of the fabricated MOSFET with FG annealing (FGA) in this study. It shows a typical MOSFET operation curve with a clear ON/OFF transition. Figure 3 shows the output characteristics ( $I_D$  vs drain voltage  $V_D$ ) of the MOSFET with  $N_2$  annealing and FGA. The MOSFET with FGA exhibits higher current drivability than the MOSFET with  $N_2$  annealing. Figure 4 shows  $\mu_{FE}$  of the fabricated MOSFETs with (solid line) and without (dotted line) FGA. By introducing the FGA, peak  $\mu_{FE}$  was improved, typically at a low  $V_G$  corresponding to a low electric field region. The peak  $\mu_{FE}$  of 160 cm<sup>2</sup>/Vs is 22% higher than our previous study (131 cm<sup>2</sup>/Vs) with  $N_2$  annealed gate stack [3]. To clarify the origin of ON-current enhancement, we compare parasitic resistance and channel resistance. Figure 5 shows the device total resistance vs channel length plots for the devices with FG and  $N_2$  annealing. The parasitic resistances, corresponding to the y-axis interception of the fitting line, remain unchanged when the PDA ambient is altered. On the other hand, channel resistance ( $R_{ch}$ ), corresponding to the slope of the fitting line, is reduced by introducing FGA. These results (Figs. 4 and 5) suggest that the Coulomb scattering at the low electric field is well suppressed due to the improvement of the gate stack quality. Similar to the previous study on the FGA effect for a MOS capacitor with CVD-SiO<sub>2</sub> on 3C-SiC [4], FGA is also efficient for plasma-oxidized and sputter-deposited SiO<sub>2</sub>, thereby improving  $\mu_{FE}$ .

© IWDTF2025 - PS-03 -

PS-03 IWDTF2025

#### 4. Conclusions

We confirmed the effectiveness of the FGA for 3C-SiC n-MOSFET. FGA is effective in reducing the channel resistance under on-state conditions. The peak  $\mu_{FE}$  of 160 cm<sup>2</sup>/Vs for the MOSFET with FGA is 22% higher than that of the N<sub>2</sub> annealed MOSFET. These results will be helpful guidelines for various 3C-SiC device applications.

#### Acknowledgements

This work was partially supported by Cooperative Research Projects in RIEC, Tohoku Univ. (No. R06/A06).

#### References

[1] S. Nishino et al., APL, 42 (1983) 460. [2] R. Oka et al., JJAP, 59 (2020) SGGD17. [3] K. Yamamoto et al., APEX, 15 (2022) 071008. [4] P. Fiorenza et al., JAP, 132 (2022) 245701.

6

Fig. 1 Cross-sectional illustration and the fabrication procedure of 3C-SiC n-MOSFET in this study.

Fig. 2 Transfer characteristics of 3C-SiC n-MOSFET with FGA.

Fig. 3 Output characteristics of 3C-SiC n-MOSFETs with FGA and N<sub>2</sub> annealing.

Fig. 4 Field-effect mobility vs  $V_G$  for the 3C-SiC n-MOSFETs with FGA and  $N_2$  annealing.

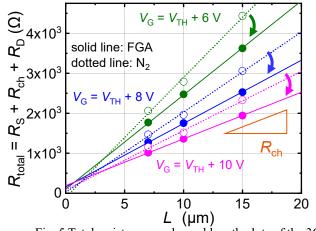

Fig. 5 Total resistance vs channel length plots of the 3C-SiC n-MOSFET for channel resistance calculation.

© IWDTF2025 - PS-03 -

PS-04 IWDTF2025

## IGZO Transistors with 700 °C Thermal Budget for Advanced DRAM Applications

Nannan You<sup>1,2#</sup>, Tianhao Liao<sup>1,2#</sup>, Jiayi Wang<sup>1,2</sup>, Yang Xu<sup>1,2</sup>, Shengkai Wang<sup>1,2\*</sup>

<sup>1</sup>State Key Laboratory of Fabrication Technologies for Integrated Circuits, Chinese Academy of Sciences, Beijing, 100029, China; <sup>2</sup> Institute of Microelectronics of Chinese Academy of Sciences, Beijing 100029, China;

\*E-mail: wangshengkai@ime.ac.cn; #Equally contributed

#### 1. Introduction

The 1T1C architecture utilizing AOS materials provides high storage density and low power consumption. Achieving its potential requires overcoming the high thermal budget ( $\sim$ 700 °C) needed for capacitive processes during the integration [1-3]. Key obstacles include leakage from crystallized high-k dielectrics and performance degradation due to interfacial atomic interdiffusion. In this work, by co-engineered HfAlO gate dielectric with an Al<sub>2</sub>O<sub>3</sub> interlayer, we demonstrate amorphous IGZO transistors that withstand 700 °C with superior performance.

#### 2. Experimental Process

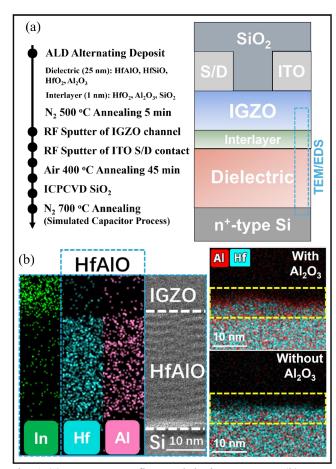

Fig. 1(a) shows the device structure. IGZO transistor fabrication began with atomic layer deposition (ALD) at 250 °C of a 25 nm HfAlO dielectric layer on n<sup>+</sup>-Si, followed by a 1 nm Al<sub>2</sub>O<sub>3</sub> interlayer. A 5-min N<sub>2</sub> anneal at 500 °C homogenized the HfAlO stack. A 15 nm IGZO channel and 25 nm ITO source/drain electrodes (defined by shadow mask) were deposited via RF sputtering. Finally, a 45-min anneal at 400 °C was performed in the air. The study compared dielectric materials (HfAlO, HfSiO, HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>) and interlayers (HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>). A 700 °C N<sub>2</sub> anneal was applied to simulate the capacitor process temperature.

#### 3. Results and Discussion

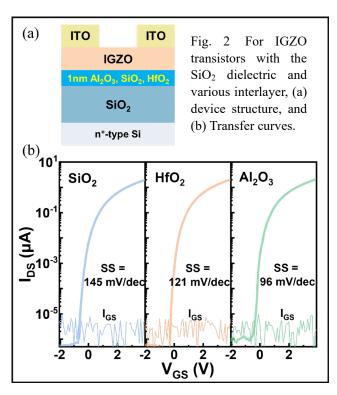

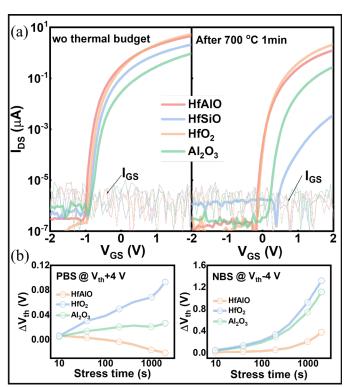

The interlayer should ensure interfacial compatibility while suppressing dielectric-channel interdiffusion. Thermodynamic and ab-initio molecular dynamics (AIMD) simulations (data not shown) indicated that Al<sub>2</sub>O<sub>3</sub> maintains a stable electronic structure, crucial for electrical consistency. Fig.1(b) TEM/EDS confirmed the Al<sub>2</sub>O<sub>3</sub> interlayer effectively suppressed interdiffusion. Experimentally, IGZO transistors with Al<sub>2</sub>O<sub>3</sub> interlayer achieved the steepest SS (96 mV/dec), as shown in Fig. 2(b),validating its superior performance and aligning with theoretical predictions.

Achieving a high thermal budget necessitates dielectrics that are uniform, amorphous, and possess a high crystallization temperature. TEM/EDS revealed uniform dielectric composition but greater Si diffusion than Al into the IGZO after  $700^{\circ}$ C annealing (data not shown), generating defects. While IGZO transistors exhibited initially comparable performance (Fig. 3a),  $700^{\circ}$ C annealing caused severe degradation in HfSiO devices. In contrast, devices with HfAlO maintained stable performance and demonstrated superior bias stress stability (Fig. 3b). HfAlO's uniformity, high k, and thermal stability establish it as the superior gate dielectric.

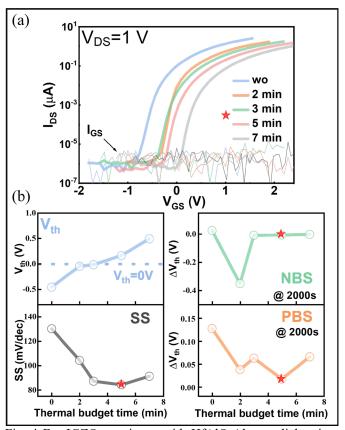

To validate the co-engineered gate stack approach, we fabricated IGZO transistors with HfAlO dielectric-Al<sub>2</sub>O<sub>3</sub> interlayer (HfAlO-Al) stacks. Devices subjected to 0-7 min annealing (Fig. 4a) showed progressive positive  $V_{th}$  shifts while maintaining relatively stable SS and minimal gate leakage. Critical parameter analysis (Fig. 4b) revealed optimal performance at 5 min: the steepest SS (84 mV/dec) and exceptional stability (+17 mV PBS, -7 mV NBS @ $\pm$ 3.8 MV/cm for 2000 s). Therefore, through co-engineering, the HfAlO-Al IGZO transistor achieves the 700 °C thermal budget for 5 min with superior performance.

#### 4. Conclusions

This work presents the 700 °C-compatible IGZO transistors, enabled by a co-engineered HfAlO-Al gate stack. This material provides a high k dielectric, a thermally stable interlayer, and a sharp interface with suppressed diffusion. Devices show exceptional stability, providing a new solution for high-density 1T1C integration.

## Acknowledgements

This work was supported by the International Partnership Program (for Future Network) of the Chinese Academy of Sciences Grant No. 102GJHZ2022066FN.

#### References

- [1] P. Mukhopadhyay., IEEE TED, 2024, VOL. 71, NO. 3.

- [2] X. Li et al., Symp. on VLSI, 2025, T17-3.

- [3] J. Lin et al., IEEE EDL, 2024, VOL. 45, NO. 10.

© IWDTF2025 - PS-04 -

PS-04 IWDTF2025

Fig. 1 (a) Key process flow and device structure, (b) TEM cross-sectional image and EDS mapping of IGZO taransitors with and without Al<sub>2</sub>O<sub>3</sub> interlayer.

Fig. 3 For IGZO transistors with various dielectrics, (a) Transfer curves and (b) Bias stress stability.

Fig. 4 For IGZO transistors with HfAlO-Al gate dielectric at 700 °C thermal budget, (a) Transfer curves and (b) Extracted critical parameter vs. thermal budget time.

PS-05 IWDTF2025

# Influence of Ar/O<sub>2</sub> ratio during IGZO deposition on the electrical characteristics of a-IGZO metal-insulator-metal diodes<sup>-</sup>

Chih-An Chen, Bai-Jun Guo, Chang-Yi Yen, Yu-Hung Chen

Department of Microelectronics Engineering, National Kaohsiung University of Science and Technology

Kaohsiung City 811213, Taiwan

Email: yhchen@nkust.edu.tw

#### 1. Introduction

This study employed RF sputtering to fabricate metal-insulator-metal (MIM) tunneling diodes, exploring the feasibility of amorphous indium gallium zinc oxide (a-IGZO) as the insulating layer beyond its conventional applications in displays and touch panels. The oxygen flow ratio during deposition and the post-annealing temperature were systematically varied, and the electrical characteristics were analyzed through device measurements. For the first time, key MIM diode parameters [1] such as asymmetry, nonlinearity, and responsivity were introduced for a-IGZO-based devices, along with a ideality factor (N) to evaluate performance. Comparative analysis was conducted to assess device characteristics under different oxygen flow and annealing conditions.

#### 2. Experimental Procedure

FTO and glass substrates were cut to size and sequentially cleaned in acetone, isopropanol, and deionized water by ultrasonic agitation (10 mins each), followed by N<sub>2</sub> drying and baking at 100 °C. a-IGZO thin films were deposited by RF sputtering at a base pressure of  $5 \times 10^{-6}$  Torr. The IGZO film was deposited as a function of the gas flow rate of argon and oxygen (Ar/O<sub>2</sub>) of 39.2:0.8, 38:2, and 36:4 sccm, respectively. Deposition parameters were adjusted to obtain the desired thickness (~10 nm), which was verified by Alpha Step measurements. The FTO/a-IGZO structures were then annealed by rapid thermal annealing (RTA) at  $5 \times 10^{-3}$  Torr, and Al top electrodes (~100 nm) were subsequently deposited by thermal evaporation under  $5 \times 10^{-6}$  Torr, forming the FTO/IGZO/Al devices. The electrical properties were characterized by I–V measurements, Hall effect, and four-point probe analysis.

#### 3. Results and Discussion

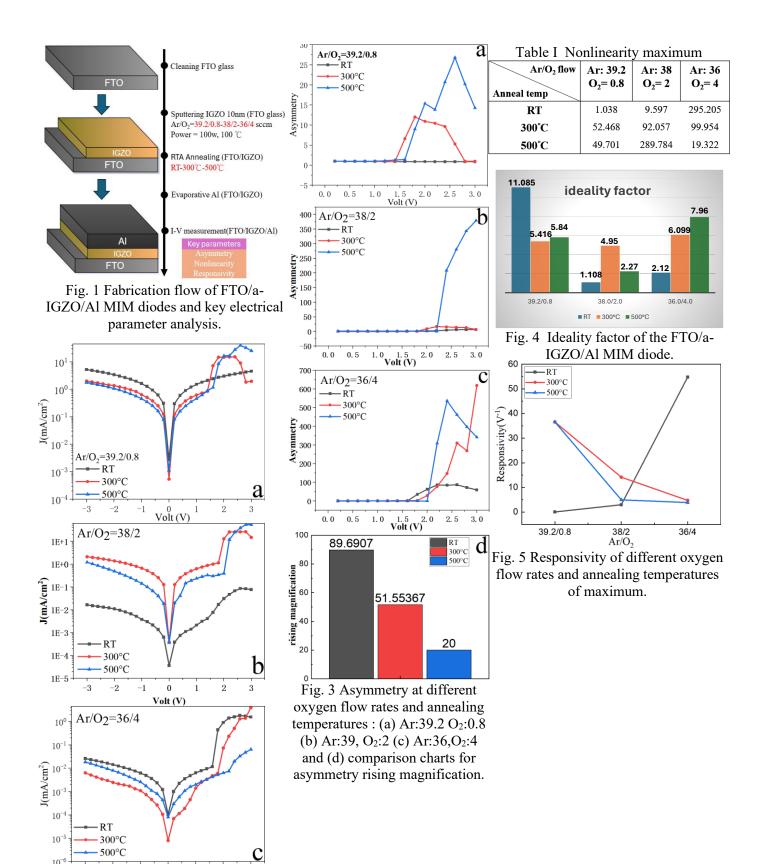

Figure 2 shows that the I–V characteristics depend on the argon/oxygen (Ar/O<sub>2</sub>) flow ratios of 39.2:0.8, 38:2, and 36:4 sccm. At low oxygen (Ar/O<sub>2</sub> = 39.2:0.8), the annealed device shows nearly Ohmic behavior (see Fig. 2a), whereas increasing oxygen to 2 sccm yields typical MIM diode behavior, with the highest ON/OFF ratio obtained at Ar/O<sub>2</sub> = 36:4. In figures 3a–3c shows that the maximum asymmetry values at room temperature are 0.97 and 87.16, whereas at 500 °C they are 26.83 and 536.57, yielding asymmetry rising magnification of 89.69 and 20 (see Fig. 3d). This indicates that the asymmetry is highly sensitive to temperature. However, both Ar/O<sub>2</sub> of 39.2:0.8 and Ar/O<sub>2</sub> of 36:4 show asymmetry degradation at higher bias(see Fig. 3a and 3c), which correlates with larger ideality factors (N = 5.84 and 7.96) and may result from microcrystallization or oxygen release in a-IGZO [2]. Table I. and Figure 5 indicate that larger ideality factors correspond to stronger nonlinearity, consistent with the defect-rich conditions at Ar/O<sub>2</sub> = 39.2:0.8 and 36:4. In contrast, samples with fewer defects show weaker correlation. Turn-on voltage is almost unaffected at lower oxygen flow but becomes more sensitive at higher oxygen flow, while excessive oxygen (Ar/O<sub>2</sub> of 36:4) reduces nonlinearity. Finally, Figure 5 shows that the maximum responsivity is achieved at Ar/O<sub>2</sub> of 36:4 at room temperature.

#### 4. Conclusions

Device performance improves as oxygen flow reduces defects, but excessive oxygen introduces interface states and instability. Annealing enhances performance up to an optimum level, beyond which a-IGZO degrades. The best condition is achieved at Ar/O<sub>2</sub> of 36:4 with annealing at 300 °C.

#### References

- [1] K. P. Musselman et al., Adv. Funct. Mater. 29, 1805533 (2019).

- [2] Tsung-Cheng Tie et al., Crystals. 13, 1310, (2023).

© IWDTF2025 - PS-05 -

PS-05 IWDTF2025

Fig. 2 I–V characteristics of the Ar/O<sub>2</sub>-sputtered IGZO MIM devices with respect to various annealing temperatures.

Volt (V)

© IWDTF2025 - PS-05 -

PS-06 IWDTF2025

# Effect of annealing temperature on the electrical characteristics of Al/CuO/p-Si MOS capacitors

Siang-Yi Hong, Xiao-Xuan Zeng, Pei-Hsuan Su, Yu-Hung Chen

Department of Microelectronics Engineering, National Kaohsiung University of Science and Technology,

Kaohsiung City 811213, Taiwan

Email: yhchen@nkust.edu.tw

#### 1. Introduction

Copper oxide (CuO) owing to its natural abundance, non-toxicity, low cost, and promising electrical and optical properties. CuO is a p-type semiconductor with a monoclinic crystal structure and a bandgap ranging from 1.2 to 2.16 eV. Various deposition techniques, including chemical bath deposition, pulsed laser deposition, and radio frequency (RF) magnetron sputtering, have been employed for the fabrication of CuO thin films.[1] Among these methods, sputtering is widely recognized for producing semiconductor thin films of superior quality, particularly in terms of reproducibility and reliability. The impact of different annealing temperatures on the structural, chemical, optical, and MOS properties of radio frequency (RF) magnetron sputtered CuO passivation layers on high-performance Si-based MOS capacitors was reported in this work.

#### 2. Experimental Procedure

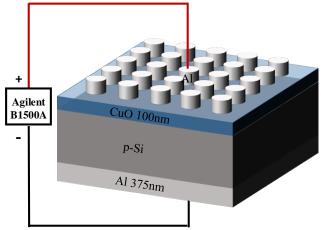

The copper oxide films were grown at room temperature by reactive magnetron sputtering. By using acetone, ethanol, and deionized water, the silicon substrates were rinsed ultrasonically. By blowing nitrogen gas, these substrates were dried in case of deposition. First, 375 nm of aluminum was deposited on the backside of the p-Si and annealed in air at 500 °C for 2 minutes to serve as the back electrode. In the experiment, a CuO target of 3 inches with 99.99% purity was used. The rotation rate of 12 rpm was fixed during the deposition. The vacuum chamber was evacuated until the base pressure reached 20 mTorr. Mixed argon—oxygen was used as the reactive gas. The oxygen flow rate was 0.05sccm, while the argon flow rate was kept at 20 sccm. Then, circular electrodes with a diameter of 0.15 mm and a thickness of 150 nm were deposited by thermal evaporation. This work using a deposition recipe of room temperature and studied the effect of post-deposition annealing temperature at 150°C, 250°C, and 350°C for 30 minutes on the electronic properties.(see Fig.1)

#### 3. Results and Discussion

The Tauc plot, C-V and I-V characteristics of the fabricated Al/ CuO/ p-Si structures were investigated.

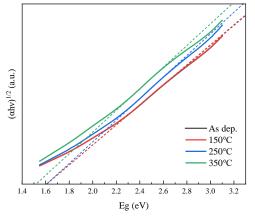

The optical gaps can be determined from the Tauc plot  $((\alpha hv)^{1/2} \text{ vs Eg})$ . This is in contrast to the electronic band gap of the material since the presence of shallow defect states can change the optical gap . The optical band gap is found to decrease substantially, moving from 1.61 eV for the as-deposited film to 1.51 eV for the film annealed at 350 °C. For the annealing temperature at 150 °C and 250 °C, the value is mostly insensitive. [2][3] (see Fig.2)

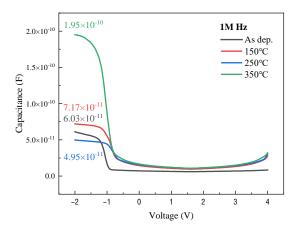

All electrical measurements were performed at room temperature using an Agilent B1500A semiconductor device analyzer. The dc bias voltage swept from -2 to 4 V, whereas the C–V measurements were performed in the frequency of 1 MHz.

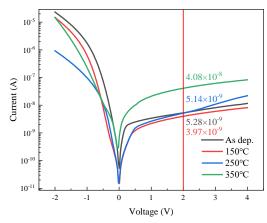

Based on the I–V measurements, it was observed that the sample annealed at  $150^{\circ}$ C exhibited the lowest leakage current of  $3.97 \times 10^{-9}$  A. An overall decrease in rectification ratio is observed with higher annealing temperatures, except at  $350^{\circ}$ C where an upward trend occurs. By using Cheung's function [4], the barrier heights were found to be 0.74 eV for both the as-deposited sample and the sample annealed at  $150^{\circ}$ C, while the values were 0.79 eV and 0.76 eV for the samples annealed at  $250^{\circ}$ C and  $350^{\circ}$ C, respectively.(see Fig.3)

The C–V characteristics revealed that the sample annealed at 350°C exhibited a higher capacitance value of 1.95  $\times$  10<sup>-10</sup> F.[5](see Fig.4)

### 4. Conclusions

Copper oxide thin films were successfully grown by magnetron sputtering, and the measurement results agreed well with the experimental predictions. Al/CuO/p-Si structure were fabricated and analyzed through optical and electrical measurements. The optical band gap decreased from 1.61 eV (as-deposited) to 1.51 eV after annealing at 350 °C, suggesting the influence of defect states.I–V analysis showed the lowest leakage current ( $3.97 \times 10^{-9}$  A) at 150 °C, while the rectification ratio decreased with annealing but slightly recovered at 350 °C. Cheung's method revealed barrier heights ranging from 0.74 to 0.79 eV depending on the annealing temperature. From the C–V

© IWDTF2025 - PS-06 -

PS-06 IWDTF2025

measurements, it can be concluded that after annealing, the shift trend became more consistent, and a more pronounced increase in capacitance was observed for the sample annealed at 350°C.

#### References

- [1] B. Balamurugan et al., Thin Solid Films **396**, pp. 90-96 (2001).

- [2] A. M. Koshy et al., J Mater Sci: Mater Electron 33, pp. 13539-13546 (2022).

- [3] W. Zeng et al., Materials 11, pp. 1253 (2018).

- [4] L. Xu et al., Physica B: Condensed Matter **673** (2024).

- [5] G. Ersöz et al., IEEE Transactions on Electron Devices 63, pp. 2948-2955 (2016).

Fig. 1 Shows the schematic diagram of the device structure.

Fig. 3 I-V plot of annealing temperature of  $150^{\circ}\mathrm{C}$  ,  $250^{\circ}\mathrm{C}$  ,  $350^{\circ}\mathrm{C}$  and non-annealing.

Fig. 2 Tauc plots of annealing temperature of 150°C, 250°C, 350°C and non-annealing.

Fig. 4 C-V plot of annealing temperature of  $150^{\circ}$ C ,  $250^{\circ}$ C ,  $350^{\circ}$ C and non-annealing.

© IWDTF2025 - PS-06 -

PS-07 IWDTF2025

# Effects of Interface Formation Process on Tunneling Current Components of N-type Ti<sub>0.3</sub>Zn<sub>0.7</sub>O<sub>1.3</sub>/P-type Si Stack Structure

Kenta Ogawa<sup>1,2\*</sup>, Toyohiro Chikyow<sup>2</sup>, Atsushi Ogura<sup>1,3</sup> and Takahiro Nagata<sup>2,1\*</sup>

<sup>1</sup> Graduate School of Science and Technology, Meiji University, Kawasaki, Kanagawa 214-8571, Japan

<sup>2</sup> National Institute for Materials Science (NIMS), Tsukuba, Ibaraki 305-0044, Japan

<sup>3</sup> Meiji Renewable Energy Laboratory, Meiji University, Kawasaki, Kanagawa 214-8571, Japan

\*E-mail: ce241031@meiji.ac.jp, NAGATA.Takahiro@nims.go.jp

#### 1. Introduction

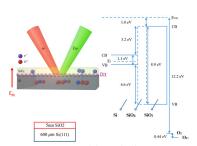

Currently, electrical devices are required to reduce power consumption and increase functionality. Tunnel field effect transistors (TFETs) allow devices to reduce power consumption and operate quickly thanks to achieve subthreshold swing values (S.S.) smaller than 60 mV/dec which is the theoretical limit of conventional Si-MOSFETs, by taking advantage of the electron tunneling effect [1,2]. Recently, bilayer structure TFETs combining amorphous ZnSnO, a n-type oxide semiconductor (n-OS), and Si, a p-type group IV semiconductors, have been proposed. It was effective that channel layer has amorphous structure to improve the performance of TFETs, because of the high film uniformity. However, further reduction of S.S. have been disturbed by the existence of oxygen defects and tail-states near conduction band minimum on oxide semiconductors due to the amorphous structure [3]. To resolve this trade-off, we have investigated  $Ti_{0.3}Zn_{0.7}O_{1.3}$  which is ZnO-based solid solution with Ti having high oxygen bond dissociation energy. As a result, we confirmed that the  $Ti_{0.3}Zn_{0.7}O_{1.3}$  film with an initial  $TiO_2$  layer in a  $TiO_2/ZnO$  multiple stacked structure formed the most uniform unintentional interfacial  $SiO_2$  layer [4]. Our next challenge is to investigate the effects of differences in interface structure on tunneling current characteristics and indicate the relationship. In this study, we report the results of evaluating the temperature and electric field dependence of the I-V characteristics of  $Ti_{0.3}Zn_{0.7}O_{1.3}/Si$  junctions which are fabricated by two interface formation processes, and qualitatively analyzing the band-to-band tunnelling (BTBT) current and trap-assisted tunnelling (TAT) current components.

#### 2. Experimental Procedure

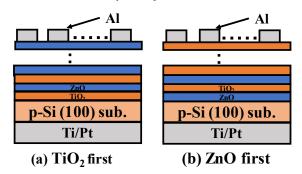

Fig. 1 shows a schematic diagram of the prepared sample.  $Ti_{0.3}Zn_{0.7}O_{1.3}$  films with an initial (a)  $TiO_2$  layer or (b) ZnO layer in a 3:7 ratio of  $TiO_2$ /ZnO multiple stacked structure on p-Si substrates (carrer concentration:  $\sim 10^{19}$  cm<sup>-3</sup>) were deposited by laser ablation (PLD) with a KrF excimer laser ( $\lambda$ =248 nm). Here, each single layer is consisted of less than mono-atomic layer and each fabrication method is referred to as (a)  $TiO_2$  first and (b) ZnO first. The total film thickness was set to 5 nm, respectively. Other conditions were oxygen pressure of  $10^{-4}$  Torr and substrate temperature of 300 °C. For electrical measurement, Al top electrodes with a diameter of 100  $\mu$ m were formed by vacuum evaporation using a metal mask and Ti/Pt back electrodes were formed by DC sputtering overall. Finally, forming gas annealing treatment (4%  $H_2$ :  $N_2$  atmosphere) at 400 °C for 30 min was carried out.

The temperature dependence of electrical properties was evaluated using I-V measurements with a cryostat at temperatures ranging from 60 K to 300 K, with a voltage step of 20 mV.

#### 3. Results and Discussion

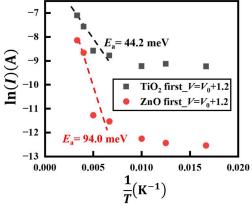

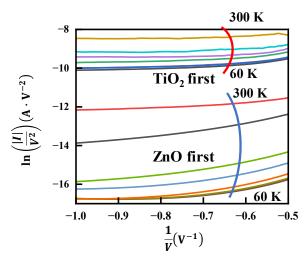

First, we evaluated the temperature dependence of the I-V characteristics of the both samples. As a result, a rise in current was confirmed even when a reverse bias was applied regardless of the fabrication process or temperature. Therefore, we analyzed the electric field dependence of the BTBT current in the reverse bias region, and that existence was observed shown in Fig.2. In addition, the BTBT barrier was lower in the TiO<sub>2</sub> first from the slope of the graph were confirmed. Furthermore, the electric field dependence of the TAT current was analyzed and that existence was also observed. This indicates the presence of tail states that contribute to electron traps in the interfacial SiO<sub>2</sub> layer or oxide semiconductor and at the interface. To quantitatively evaluate the depth of this trap level, the arrhenius plot analysis was performed, as shown in Fig. 3 [5]. We found that the activation energy of TiO<sub>2</sub> first was significantly lower than that of ZnO first in this study and the ZnSnO TFET in previous study [3]. The reduction in the BTBT barrier and activation energy in TiO<sub>2</sub> first can be explained by the difference in interfacial properties. We have already revealed that TiO<sub>2</sub> first prevents the formation of metal silicate microcrystallites and forms an interface layer with low roughness than ZnO first

© IWDTF2025 - PS-07 -

PS-07 IWDTF2025

by the effects of high oxygen bond dissociation energy of Ti, and this is thought to suppress deep trap states in the interface and oxide semiconductor layer [4].

#### 4. Conclusions

To investigate the relationship between the interface formation process and the tunneling current characteristics, we evaluated the temperature and electric field dependence of the tunneling current components in two types of  $Ti_{0.3}Zn_{0.7}O_{1.3}/Si$  junctions with defferent fabrication processes. As a result, we found that  $TiO_2$  first/Si, which has an interface layer with less microcrystal formation and low roughness, has the smaller BTBT barrier and activation energy, and can suppress electron trapping at the interface. This result suggests that the increase in on-current of TFETs and the reduction of S.S. can be realized by optimizing the interface formation process and suppressing trap states in the interface and oxide semiconductor layer.

### Acknowledgements

A part of this work was supported by "Advanced Research Infrastructure for Materials and Nanotechnology in Japan (ARIM)" of the Ministry of Education, Culture, Sports, Science and Technology (MEXT) [Proposal Nos. JPMXP1223NM5168 and JPMXP1224NM5066], and by the JST-Mirai Program [Grant No. JPMJMI21G2], Japan.

#### References

- [1] S. Takagi et al., VLSI symp., 3, T22 (2015).

- [2] S. Takagi et al., Solid State Electron., 125, 82 (2016).

- [3] K. Kato et al., IEEE J. Electron Devices Soc., 7, 1201 (2019).

- [4] K. Ogawa et al., Jpn. J. Appl. Phys., 64, 05SP25 (2025).

- [5] S. M. Sze et al., Physics of Semiconductor Devices (Wiley, New York, 2021) 2nd ed. p. 402 Part 3, Chap. 7.

Fig. 1 Schematic diagram of Ti<sub>0.3</sub>Zn<sub>0.7</sub>O<sub>1.3</sub>/Si sample structures for (a) TiO<sub>2</sub> first, and (b) ZnO first.

Fig. 3 Arrhenius plots of TiO<sub>2</sub> first and ZnO first/Si.

Fig. 2 Electric field dependence of the BTBT current with TiO<sub>2</sub> first and ZnO first/Si.

© IWDTF2025 - PS-07 -

PS-08 IWDTF2025

## Classical Molecular Dynamics Simulation of Ferroelectric Properties of a-HfO<sub>2</sub>

Jumpei Ohba, Sora Yamamoto, Yusuke Nishimura, Takanobu Watanabe Faculty of Science and Engineering, Waseda University, 3-4-1 Okubo, Shinjuku, Tokyo 169-8555 Japan Email:junpeita@akane.waseda.jp / Phone: +81-90-9376-9358

#### 1. Introduction

HfO<sub>2</sub> thin films have been reported to exhibit ferroelectricity even at film thicknesses of several nanometers [1,2] and are attracting attention as next-generation nonvolatile memory materials. The origin of the ferroelectric property of HfO<sub>2</sub> film is attributed to the Pca2<sub>1</sub> phase [3], but there are still many unresolved issues, such as the mechanisms by which residual polarization depends on impurity doping and rapid thermal treatment. Several authors reported molecular simulation studies on the ferroelectricity of HfO<sub>2</sub> crystals [4] by using first-principles molecular dynamics (MD) and on the structural phase transition of HfO<sub>2</sub> [6] by using a machine learning MD (DeepMD) [5]. However, no MD simulation has been reported that reproduces the ferroelectricity of HfO<sub>2</sub> at sizes of several nanometers or larger, which are close to real thin films.

In this study, we performed classical MD calculations of HfO<sub>2</sub> applying an external electric field. We employed the Born-Mayer-Huggins (BMH) potential [7-10], which is one of simplest interatomic interaction models representing ionic bonding. Significant hysteresis has been reproduced in an amorphous HfO<sub>2</sub> (a-HfO<sub>2</sub>) model.

#### 2. Experimental Procedure

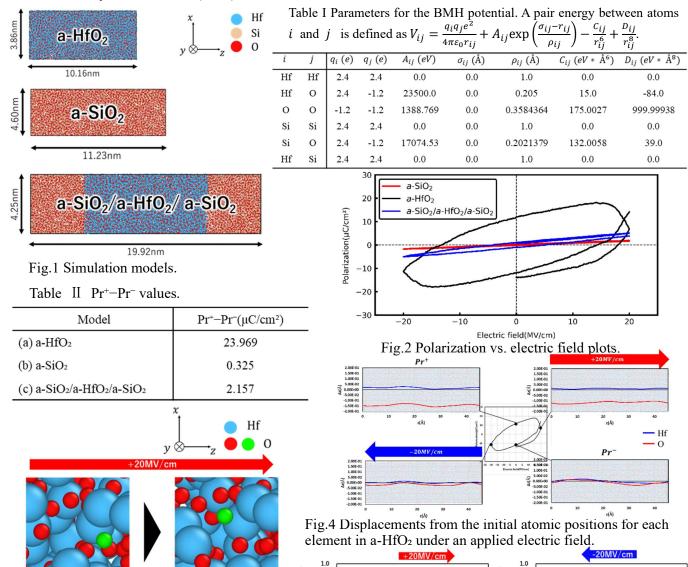

Fig. 1 shows the model used in the MD simulation: (a) bulk a-HfO<sub>2</sub>, (b) bulk a-SiO, and (c) a-SiO<sub>2</sub>/a-HfO<sub>2</sub>/a-SiO<sub>2</sub> interface structures. Three-dimensional periodic boundary condition is posed for all models. These amorphous structures were generated by melting the crystalline HfO<sub>2</sub> and SiO<sub>2</sub> structures through three processes: melting at 8000 K, isothermal isobaric treatment at 1200 K, and cooling to 300 K. An electric field was applied along the z-axis (see Fig.1), and dipole moment component along z-axis was calculated. The external electric field was increased by +0.05 MV/cm every 0.3 ps until to reach +20 MV/cm. Then, it was swept back to -20 MV/cm at the same rate. Finnally, it was again increased again at the same rate to +20 MV/cm. The parameter set of the potential was determined by refitting the Morse-BKS potential for the Hf,Si,O system [10] with the BMH potential. The potential formula the parameters at that time are shown in Table I.

#### 3. Results and Discussion

Fig. 2 shows the electric field–polarization characteristics of a-HfO<sub>2</sub>, a-SiO<sub>2</sub>, and a-SiO<sub>2</sub>/a-HfO<sub>2</sub>/a-SiO<sub>2</sub> interface structures. A clear hysteresis is reproduced in the a-HfO<sub>2</sub> model. The difference between maximum and minimum residual polarization was  $Pr^+-Pr^-=24~\mu C/cm^2$ . The polarization was calculated by the displacement of each ion from its initial position. Figure 3 shows the displacement of oxygen ions when an electric field is applied. The O ions predominantly undergo plastic deformation in the opposite direction to the applied electric field. Figure 4 shows the displacement for each element as a function of original z-position. It can be seen that the contribution of O ion movement is overwhelmingly greater than Hf.

The a-SiO<sub>2</sub>/a-HfO<sub>2</sub>/a-SiO<sub>2</sub> layered model also exhibits a smaller hysteresis of approximately  $Pr+-Pr-\approx 4$   $\mu C/cm^2$ . The reduction in the ferroelectric hysteresis is considered to be the depolarization due to polarized charges appeared at a-HfO<sub>2</sub>/a-SiO<sub>2</sub> interfaces. Fig. 5 shows the charge distribution and internal electric field distribution along z-axis when an electric field of  $\pm 20$  MV/cm is applied. The positive and negative charges in the dipole layers at both interfaces are asymmetrical, and their relative magnitudes are reversed between the  $\pm 20$  MV/cm and  $\pm 20$  MV/cm. This can be interpreted as the induced polarization charges being superimposed on the dipoles at a-HfO<sub>2</sub>/a-SiO<sub>2</sub> interfaces. The altered charge distribution within the interface dipole layer generates an electric field within the HfO<sub>2</sub> layer opposite to the external electric field, thereby weakening the ferroelectric hysteresis of the a-HfO<sub>2</sub> layer as a ferroelectric material.

#### 4. Conclusions

We demonstrated that the ferroelectricity of a-HfO<sub>2</sub> film can be simulated in large scale by means of classical molecular dynamics employing a very simple, pairwise interaction for ionic materials. Origin of the ferroelectricity has been confirmed as the plastic deformation of O ions upon the external electric field application. In the a-SiO<sub>2</sub>/a-HfO<sub>2</sub>/a-SiO<sub>2</sub> layered structure, the polarization charge appears at the interfaces, thereby the charge distribution in the interface dipole layer altered. Since the employed BMH potential can handle various kinds of metal cations simultaneously, our approach is considered effective for studying the effects of heterogeneous interfaces and impurities in ferroelectric HfO<sub>2</sub> films.

© IWDTF2025 - PS-08 -

**PS-08** IWDTF2025

#### Acknowledgements

This research was supported by Grants-in-Aid for Scientific Research (23K22800, 25K01295) and partly executed under the cooperation of organization between Kioxia Corporation and Waseda University.

#### References

[1] A. Toriumi, Appl. Phys. 88, 586 (2019). [2] X. Tian et al., APL 112, 102902 (2018). [3] T. Shimizu t al., APL 107, 032910 (2015). [4] P. Fan, et al., J. Chem. Phys. 35, 21743 (2019). [5] L. Zhang et al., PRL 120, 143001 (2018). [6] J. Wu et al., PRB 103, 024108 (2021). [7] F. G. Fumi et al., J. Phys. Chem. Solids. 25, 31(1964). [8] M/. P. Tosi et al., J. Phys. Chem. Solids. 25, 45 (1964). [9] M. Matsui, Phys. Chem. Miner. 23, 345 (1996). [10] J. P. Trinastic, et al., J. Chem. Phys. 139, 154704 (2013).

0.5  $(10^2C/cm^3)$ 0.0

-0.5

Electric field (MV 10 Z (nm)

Fig.3 Displacement of oxygen ions in a-HfO<sub>2</sub> when an electric field is applied.

Fig.5 Charge and local electric field profiles of a-SiO<sub>2</sub>/a-HfO<sub>2</sub>/a-SiO<sub>2</sub> under external fields of (a) +20MV/cm (b) -20MV/cm.

0.0

-0.5

10 Z (nm)

© IWDTF2025 - PS-08 - PS-09 IWDTF2025

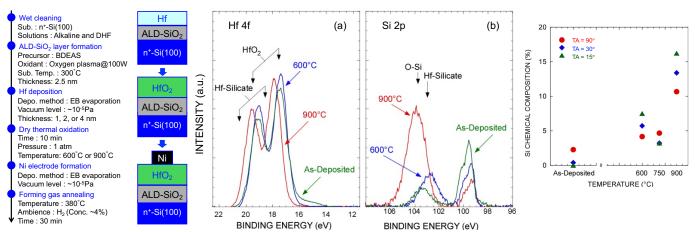

# Effects of Al Concentration and Annealing Method on Crystalline and Ferroelectric properties of Al:HfO<sub>2</sub> Thin Films

Tomoya Mifune<sup>1</sup>, Hideaki Tanimura<sup>1,2</sup>, Yuma Ueno<sup>2</sup>, Yusuke Tani<sup>2</sup>, Yukiya Sano<sup>1</sup>, Hironori Fujisawa<sup>1</sup>, Seiji Nakashima<sup>1</sup>, Ai I. Osaka<sup>1</sup>, Shinichi Kato<sup>2</sup> and Takumi Mikawa<sup>2</sup>

<sup>1</sup>Univ of Hyogo, <sup>2</sup> SCREEN Semiconductor Solutions

<sup>1</sup>Shosha 2167, Himeji, Hyogo 671-2280, Japan, <sup>2</sup>Takamiya-cho 480-1, Hikone, Shiga 522-0292, Japan Email: ei24i023@guh.u-hyogo.ac.jp / Phone: +81-79-267-4883

#### 1. Introduction

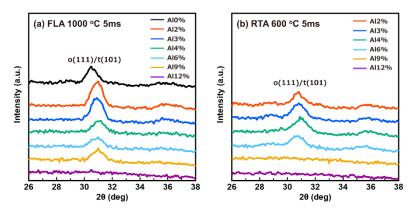

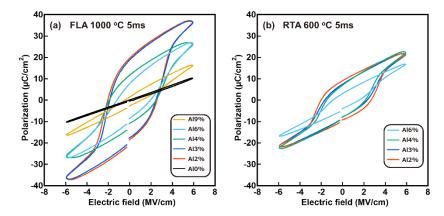

HfO<sub>2</sub>-based ferroelectrics have attracted considerable attention as promising candidates for next-generation non-volatile devices owing to their excellent scalability and high compatibility with CMOS processes. Among them, Al-doped HfO<sub>2</sub> (HAO) exhibits high thermal stability, making it suitable for high-temperature processes, such as 3D-NAND fabrication [1]. However, HAO thin films typically require high crystallization temperatures, and conventional rapid thermal annealing (RTA) can potentially cause damage to underlying devices. To address this issue, we focused on flash lamp annealing (FLA), which enables millisecond-scale crystallization with a reduced thermal budget. Our previous work demonstrated that FLA-crystallized HAO films exhibit polarization values approximetly 1.6 times higher than those crystallized through RTA [2]. Nevertheless, the influence of Al concentration on the crystallinity and ferroelectric properties of FLA-crystallized HAO films remains insufficiently explored. In this study, we fabricated HAO thin films with Al concentrations ranging from 0 to 12 at% and systematically evaluated their crystallinity and ferroelectric properties, comparing the effects of different annealing processes.

#### 2. Experimental Procedure

TiN/HAO/TiN capacitors were fabricated on Si substrates. HAO thin films with a thickness of 10 nm were deposited by atomic layer deposition (ALD), with the Al composition ratio, Al/(Al+Hf), controlled between 0 and 12 at%. Different annealing processes were employed for crystallization: (i) FLA with a preheating temperature of 400 °C and a peak temperature of 1000 °C for 5 ms in  $N_2$  atmosphere; (ii) RTA at 600 °C for 1 min in  $N_2$  atmosphere. The crystallinity of the films was evaluated by grazing-incidence X-ray diffraction (GIXRD), and ferroelectric properties were characterized by polarization-electric field (P-E) hysteresis measurements.

#### 3. Results and Discussion

Figure 1 shows the XRD patterns of HAO films after FLA and RTA. Crystallization was observed up to 6 at% Al for RTA and up to 9 at% Al for FLA. In both processes, the peak intensity was maximized around 2-3 at% Al, indicating that this concentration range is optimal for crystallization regardless of the annealing method. Furthermore, FLA yielded higher peak intensities than RTA, suggesting improved crystallinity. Figiure 2 shows the dependence of the diffraction angle on Al concentration. As the Al content increased, the peaks shifted toward higher angles, indicating that tensile stress was induced in the film due to the substitution of smaller Al ions for Hf. FLA-crystallized films exhibited peaks at higher angles than RTA-treated films, implying that stronger tensile stress was introduced. Since tensile stress promotes the formation of the ferroelectric orthorhombic (o) phase [3], FLA is considered more effective than RTA in facilitating o-phase formation. Figiure 3 presents the P–E hysteresis loops of HAO films with varying Al concentrations. FLA-crystallized films exhibited higher polarization values than RTA-treated films, with the most significant improvement (approximately 1.4 times) observed at 2 at% Al. Taken together with the XRD results, these findings suggest that the enhanced polarization in FLA-treated films originates from the stronger tensile stress, which increases the fraction of the o-phase.

#### 4. Conclusions

Both FLA and RTA processes yielded maximum crystallinity and ferroelectricity at an Al concentration of 2 at%. FLA introduced greater tensile stress than RTA, promoting o-phase formation and enhancing polarization properties. These results demonstrate that FLA not only enables low-thermal-budget crystallization but also effectively induces tensile stress in HAO thin films, thereby improves ferroelectric performance.

© IWDTF2025 - PS-09 -

PS-09 IWDTF2025

#### References

- [1] G. Kim et al., IEDM, 5.4.1-5.4.4 (2022)

- [2] H. Tanimura et al., Jpn. J. Appl. Phys. **63**, 09SP10 (2024)

- [3] T. Song et al., Appl. Phys. Rev. 10, 041415(2023)

Fig. 1 Al concentration dependence of XRD patterns. HAO films crystallized by (a) FLA and (b) RTA exhibited the highest peak intensity around 2-3 at% Al. FLA can crystallized HAO films up to 9 at% Al.

Fig. 2 Al concentration dependence of HAO diffraction angles. The diffraction angles shifted toward higher angles with increasing Al concentration, suggesting tensile stress.

Fig. 3 P–E hysteresis loops of HAO films with varying Al concentrations. (a) FLA- and (b) RTA-crystallized films showed the highest polarization at 2 at% Al with  $2P_r = 37.9$  and  $26.3 \,\mu\text{C/cm}^2$ , respectively.

© IWDTF2025 - PS-09 -

PS-10 IWDTF2025

# Consideration on the Coexisting Positive- and Negative-Imprinted Ferroelectric Domains and Their Imprint-Recovery in Non-Doped HfO<sub>2</sub> MFM Capacitors

Yukinori Morita, Shutaro Asanuma, Hiroyuki Ota, and Shinji Migita SFRC, AIST

Tsukuba, Ibaraki 305-8569, Japan Email: y.morita@aist.go.jp / Phone: +81-80-2216-4272

#### 1. Introduction

The HfO<sub>2</sub>-based ferroelectrics (Fe-HfO<sub>2</sub>) have attracted attention and are being studied for their potential application in memory devices. One of the challenges in memory applications is the instability of polarization (wake-up and fatigue) caused by the application of cyclic voltages. This is thought to be caused by changes in the distribution of oxygen vacancies in the Fe-HfO<sub>2</sub> film due to the cyclic electric field. Changes in the distribution of charged vacancies and interstitial oxygen are also causes of unbalanced polarization characteristics, known as imprint. These issues need to be understood and addressed.

We found that the ferroelectric non-doped HfO<sub>2</sub> prepared by changing the annealing conditions exhibited a polarization-voltage (PV) shape different from that of normal ferroelectric properties. Evaluating the change in the PV shape when applying a cyclic voltage to these samples, it was suggested that the initial imprinted state of ferroelectric domains may be recovered by applying a cyclic voltage.

#### 2. Experimental Procedure

Metal-ferroelectric-metal (MFM) capacitors were prepared with non-doped HfO<sub>2</sub> [1-3]. In the fabrication process, a Si wafer was first cleaned with diluted HF, and a 10-nm-thick bottom TaN electrode was deposited using DC sputtering. A 10-nm-thick HfO<sub>2</sub> layer was then deposited by RF sputtering using a HfO<sub>2</sub> target. A 10-nm-thick TaN top electrode was also deposited by DC sputtering. Crystallization annealing was subsequently performed at temperatures ranging from 465 to 992 °C using the rapid thermal annealing (RTA) method in a vacuum. Finally, top and bottom Al electrodes were fabricated by photolithography and dry etching.

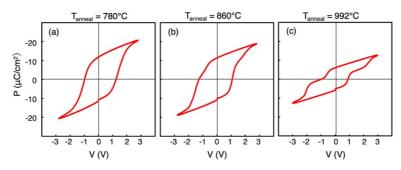

#### 3. Results and Discussion

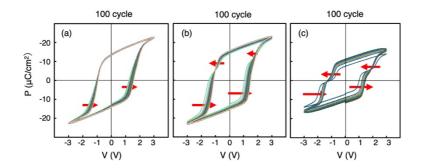

Figure 1 shows the PV characteristics of the  $HfO_2$  MFM capacitors with varying annealing temperature. By annealing at  $780^{\circ}$ C, the  $HfO_2$  capacitor exhibits ferroelectricity as shown in (a). With increasing the annealing temperature, in Fig. 1(b), the PV shape slightly changes to a polygonal-like shape, which may reflect responses in multiple domains. In Figure 1(c), the shape changes further to a polygonal-like shape, which looks like a triple state with an intermediate polarization state added. Figure 2 shows the change in the PV shape with a  $\pm 3V$  triangular pulse applied for 100 cycles to the MFM capacitors shown in Figure 1. In Figure 2(a), a noticeable shift in the lower part of the PV curve is observed due to the voltage cycle increase. Also, in Figures 2(b) and (c), the direction of the characteristic shift due to voltage cycle application is opposite between the upper and lower parts of the PV curve, which is indicated by red arrows in the figure. After these characteristic shape changes, in (b) and (c), the PV shape approaches the shape of the normal PV curve corresponding to bistable states from the polygonal-like PV mentioned in Figure 1. Figure 3 shows a model of the phenomenon in which the PV shape returns from a polygonal-like to a normal shape. We assume that a polygonal-like PV appears due to two types of domains that are previously imprinted in opposite directions by thermal annealing. The imprint is recovered by applying a voltage cycle, as shown in Fig. 3(b), causing a transition from a polygonal-like to a normal PV, which can explain the phenomenon well.

#### Acknowledgements

Part of this work was supported by JSPS KAKENHI (20H00240 and 20H02445) and JST Japan-Taiwan Collaboration Research Program (JPMJKB1903).

#### References

- [1] S. Migita, et al., Appl. Phys. Express 14 (2021) 051006.

- [2] Y. Morita, et al., Jpn. J. Appl. Phys. 63 (2024) 04SP53.

- [3] Y. Morita, et al., Jpn. J. Appl. Phys. 64 (2025) 01SP26.

© IWDTF2025 - PS-10 -

PS-10 IWDTF2025

Fig. 1 PV characteristics of MFM capacitors with non-doped HfO<sub>2</sub>. Annealing temperatures of the MFM capacitors are (a) 780, (b) 860 and (c) 992°C, respectively.

Fig. 2 Overlayed PV characteristics of MFM capacitors of non-doped HfO<sub>2</sub> with 100-cycle triangular pulse application. Red arrows indicate shift direction of the curves from 1<sup>st</sup> to 100<sup>th</sup> voltage cycles. Annealing temperatures of the MFM capacitors are (a) 780, (b) 860 and (c) 992°C, respectively.

Fig. 3 Possible model of polygonal-like PV and return of the PV shape after cyclic voltage apply. (a) Schematic model of MFM capacitor cross-section and PVs of initially imprinted domains. Sum of these PVs shows polygonal-like PV as shown in Fig. 1(c). (b) Imprint recovery in initially imprinted domains by application of voltage cycles implies shift of individual PVs. As a result, polygonal-like PV changes to normal shape.

© IWDTF2025 - PS-10 -

PS-11 IWDTF2025

# Polarization Inversion in Hf-based Oxide Layer with High Si Content in MOS Structure

Riku Kayagi<sup>1</sup>, Wataru Yasuda<sup>2</sup>, Akio Ohta<sup>3</sup>, Katsunori Makihara<sup>2</sup>, Yusuke Ichino<sup>1</sup>, Yoshiyuki Seike<sup>1</sup>, Tatsuo Mori<sup>1</sup>, and Noriyuki Taoka<sup>1</sup>

<sup>1</sup>Aichi Inst. Tech., <sup>2</sup>Nagoya Univ., <sup>3</sup>Fukuoka Univ.

<sup>1</sup>1247 Yachigusa, Yakusa-cho, Toyota, 470-0392, Japan

Email: v25707vv@aitech.ac.jp, ntaoka@aitech.ac.jp / Phone: +81-565-48-8121

#### 1. Introduction

Ferroelectric properties have been demonstrated in orthorhombic Hf-based oxide films with nanometer-scale thicknesses, achieved through precise control of the crystal structure[1]. Due to this ferroelectricity, orthorhombic Hf-based oxides have attracted significant attention as promising gate dielectric materials for steep-slope devices that can improve the subthreshold characteristics of MOSFETs. These ferroelectric Hf-based oxide layers exhibit a remanent polarization ~20  $\mu$ C/cm² with a Si doping concentration of ~1%[2]. However, this value corresponds to a charge density of ~10¹⁴ cm⁻², which is far larger than the carrier density modulated by gate voltage in a typical MOSFET. Therefore, precise control of remanent polarization as well as the MOS interface quality is crucial for realizing steep-slope devices utilizing Hf-based oxide layers.

In this study, MOS capacitors with Hf-based oxide layers were fabricated by post-oxidation of Hf layers with different initial thicknesses. The correlation between the initial Hf layer thickness and the electrical properties of the MOS capacitors was systematically investigated.

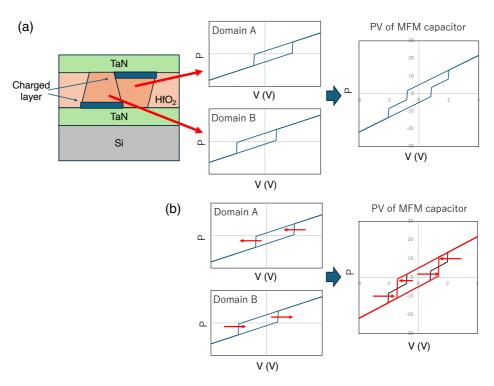

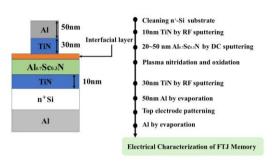

#### 2. Experimental Procedure

As shown in Fig. 1, an n<sup>+</sup>-Si(100) substrate with a resistivity of  $\leq$ 0.005  $\Omega$ ·cm was cleaned using a conventional wet cleaning process. A 2.5-nm-thick SiO<sub>2</sub> interfacial layer was then formed by atomic layer deposition (ALD) with bis(diethylamino)silane and oxygen plasma. Subsequently, Hf films with thicknesses ( $t_{\rm Hf}$ ) ranging from 1 to 4 nm were deposited by electron-beam evaporation and thermally oxidized in an oxygen ambient at 600–900 °C for 10 min using a lamp annealing system, resulting in the formation of Hf-based oxide layers. Finally, MOS capacitors were fabricated with Ni top electrodes and Al bottom electrodes. X-ray photoelectron spectroscopy (XPS) was performed after the oxidation. Their *C-V* characteristics and charge response under pulse bias were systematically evaluated.

#### 3. Results and Discussion

To clarify the chemical bonding features after the oxidation, the XPS measurements were carried out. In the Hf 4f spectra of the sample with  $t_{Hf}$  = 2 nm (Fig. 2(a)), the peaks observed at the binding energies of 19 and 21 eV show higher intensities for the oxidation at 900°C compared with those for 600°C and the as-deposited sample. Similarly, in the Si 2p spectra (Fig. 2(b)), the intensity near 103 eV is markedly enhanced at 900 °C. These results indicate the formation of Hf-silicate, which originates from Si diffusion from the Si substrate into the Hf layer. Angle-resolved XPS (Fig. 3) revealed a significant increase in Si content within the Hf-based oxide layer. After oxidation at 900 °C, the Si concentration exceeded 10%, and reached 16% at a take-off angle (TA) of 15°, suggesting that Si atoms diffuse toward the oxide surface despite the presence of the ALD-SiO<sub>2</sub> interlayer.

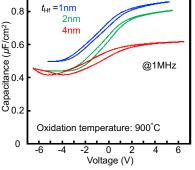

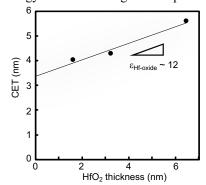

The diffusion of Si strongly affects the electrical properties of the Hf-silicate layer. Figure 4 shows the C-V curves measured at 1 MHz for  $t_{Hf}$  = 1, 2, and 4 nm after the oxidation at 900 °C. The capacitance under strong accumulation bias condition decreases with increasing  $t_{Hf}$ . From the capacitance equivalent thickness (CET) and the estimated physical thickness of HfO<sub>2</sub>, the relative permittivity was found to be ~12 (Fig. 5), which is smaller than that of ferroelectric HfO<sub>2</sub>. This is consistent with the Hf-silicate formation. In addition, clear hysteresis loops were observed in the C-V curves for all  $t_{Hf}$  values (Fig. 4). If the Hf-silicate exhibits ferroelectricity, these loops can be attributed to polarization inversion. However, C-V measurements are generally influenced by slow traps, making quantitative evaluation difficult.

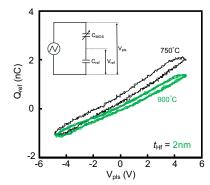

To minimize the effect of slow traps, charge responses to pulse bias ( $V_{\rm pls}$ ) were examined using a Sawyer–Tower circuit with a 1 kHz triangular pulse (Fig. 6, inset). The stored charge  $Q_{ref}$  was obtained from  $C_{\rm ref} \times V_{\rm ref}$ , where  $C_{\rm ref}$  is the reference capacitance. Since  $C_{\rm ref}$  is constant, the measured  $Q_{ref}$  reflects the capacitance of the MOS capacitors. While devices with  $t_{Hf}$  = 1 and 4 nm oxidized at 900 °C showed no hysteresis, those with  $t_{Hf}$  = 2 nm oxidized at 750 °C and 900 °C clearly exhibited hysteresis loops (Fig. 6). The change in  $Q_{ref}$  at  $V_{\rm pls}$  = 0

© IWDTF2025 - PS-11 -

PS-11 IWDTF2025

was smaller than previously reported values [2]. These findings suggest that the polarization inversion can be modulated by controlling Si diffusion and subsequent Hf-silicate formation.

#### 4. Conclusions