Program IWDTF2025

## Fri. Nov 7, 2025

Thermal Oxidation Mechanism & 2D Materials | Simulation & Characterization

苗 Fri. Nov 7, 2025 9:00 AM - 10:40 AM JST | Fri. Nov 7, 2025 12:00 AM - 1:40 AM UTC 🏛 5F-Meeting Room

## [S5] Thermal Oxidation Mechanism & 2D Materials

Chair:Takanobu Watanabe(Waseda University), Koji Kita(The University of Tokyo)

9:00 AM - 9:20 AM JST | 12:00 AM - 12:20 AM UTC [S5-01]

First-principles study of excess Si transport in Si oxide on Si substrate using two-layer-oxide model for thermally oxidized interface

\*Hiroyuki Kageshima<sup>1</sup>, Insung Seo<sup>1</sup>, Toru Akiyama<sup>2</sup>, Kenji Shiraishi<sup>3</sup> (1. Shimane University (Japan), 2. Mie University (Japan), 3. Tohoku University (Japan))

9:20 AM - 9:40 AM JST | 12:20 AM - 12:40 AM UTC [S5-02]

Oxygen Pressure Dependence of Linear-Parabolic Growth Retardation on Si(111)

\*Hengyu Wen<sup>1</sup>, Yasutaka Tsuda<sup>2</sup>, Yuki Okabe<sup>1</sup>, Akitaka Yoshigoe<sup>2</sup>, Jiayi Tang<sup>3</sup>, Yuji Takakuwa<sup>4</sup>, Shuichi Ogawa<sup>1</sup> (1. Nihon University (Japan), 2. JAEA (Japan), 3. JASRI (Japan), 4. Tohoku University (Japan))

9:40 AM - 10:00 AM JST | 12:40 AM - 1:00 AM UTC [S5-03]

Cooperation Mechanism between Single- and Double-Step Oxidation Reaction Loops during Dry Oxidation on p-Si(001) and n-Si(001) Surfaces

\*Yuki Okabe<sup>1</sup>, Yasutaka Tsuda<sup>2</sup>, Hengyu Wen<sup>1</sup>, Akitaka Yoshigoe<sup>2</sup>, Yuji Takakuwa<sup>3</sup>, Shuichi Ogawa<sup>1</sup> (1. Nihon University (Japan), 2. JAEA (Japan), 3. Tohoku University (Japan))

10:00 AM - 10:20 AM JST | 1:00 AM - 1:20 AM UTC [S5-04]

Segregation induced formation of two-dimensional like GeSn ultra-thin crystal

\*Shigehisa Shibayama<sup>1</sup>, Taiga Mtasumoto<sup>1</sup>, Akio Ohta<sup>2</sup>, Ryo Yokogawa<sup>3,4,5</sup>, Mitsuo Sakashita<sup>1</sup>, Masashi Kurosawa<sup>1</sup>, Osamu Nakatsuka<sup>1,6</sup> (1. Grad. Sch. of Eng., Nagoya Univ. (Japan), 2. Faculty of Sci., Fukuoka Univ. (Japan), 3. RISE, Hiroshima Univ. (Japan), 4. Grad. Sch. of Adv. Sci. and Eng., Hiroshima Univ. (Japan), 5. MREL (Japan), 6. IMaSS, Nagoya Univ. (Japan))

10:20 AM - 10:40 AM JST | 1:20 AM - 1:40 AM UTC [S5-05]

Role of Annealing Atmosphere Towards Stoichiometry and Chemical Integrity of Solution-Processed MoS<sub>2</sub> Thin films

\*Md Iftekharul Alam<sup>1</sup>, Shungo Nagata<sup>1</sup>, Jaehyo Jang<sup>2</sup>, Hayato Kosaka<sup>1</sup>, Naoki Matsunaga<sup>2</sup>, Yoshiteru Amemiya<sup>1</sup>, Ryo Yokogawa<sup>1</sup>, Hitoshi Wakabayashi<sup>2</sup>, Akinobu Teramoto<sup>1</sup> (1. Hiroshima Uiversity (Japan), 2. Institute of Science Tokyo (Japan))

Program IWDTF2025

Focus Session | Electrically / Physicaly Characterization

## [FB] Focus Session B ~ Device Properties under Cryogenic Temperature

Chair: Akio Ohta (Fukuoka University), Takezo Mawaki (Tohoku University)

10:55 AM - 11:25 AM JST | 1:55 AM - 2:25 AM UTC

[FB-01]

(invite)Demonstration of Recovery Annealing on 7-Bits per Cell 3D Flash Memory at Cryogenic Operation for Bit Cost Scalability and Sustainability

\*Yuta Aiba<sup>1</sup> (1. Frontier Technology Research & Development Institute., Kioxia Corporation (Japan))

11:25 AM - 11:55 AM JST | 2:25 AM - 2:55 AM UTC [FB-02]

Toward Stable Operation of Si Quantum Computers: Origin of Long-period Charge Fluctuations in Si Fin-type Quantum Dots

\*Hiroshi Oka<sup>1</sup>, Hidehiro Asai<sup>1</sup>, Kimihiko Kato<sup>1</sup>, Takumi Inaba<sup>1</sup>, Shota Iizuka<sup>1</sup>, Yusuke Chiashi<sup>1</sup>, Hitoshi Yui<sup>1</sup>, Shoko Nagano<sup>1</sup>, Shigenori Murakami<sup>1</sup>, Yoshihisa Iba<sup>1</sup>, Minoru Ogura<sup>1</sup>, Takashi Nakayama<sup>1</sup>, Hanpei Koike<sup>1</sup>, Hiroshi Fuketa<sup>1</sup>, Satoshi Moriyama<sup>2</sup>, Takahiro Mori<sup>1</sup> (1. AIST (Japan), 2. Tokyo Denki Univ. (Japan))

Power Device & Processes | Electron device, process, and characterization

**⊞** Fri. Nov 7, 2025 1:30 PM - 3:10 PM JST | Fri. Nov 7, 2025 4:30 AM - 6:10 AM UTC **Ⅲ** 5F-Meeting Room

# [S6] Power Device & Processes (1)

Chair: Motoyuki Sato (Tokyo Electron), Toshinori Numata (Toyota Technological Institute)

1:30 PM - 2:00 PM JST | 4:30 AM - 5:00 AM UTC

[S6-01]

Carbon P<sub>b</sub> centers in 4H-SiC/SiO<sub>2</sub> interface

\*Takahide Umeda Umeda<sup>1</sup>, Mitsuru Sometani<sup>2</sup>, Bunta Shimabukuro<sup>1</sup>, Yusuke Nishiya<sup>3</sup>, Yu-ichiro Matsushita<sup>3</sup> (1. Univ. of Tsukuba (Japan), 2. AIST (Japan), 3. Quemix Inc./Tokyo Univ. (Japan))

2:00 PM - 2:20 PM JST | 5:00 AM - 5:20 AM UTC

[S6-02]

Study on Possible Origin of Improved 4H-SiC (0001) MOS Interface Characteristics with Direct NO Oxynitridation Based on Consideration of Oxinitride Growth Kinetics

\*Yutaro Uchida<sup>1</sup>, Atsushi Tamura<sup>1</sup>, Koji Kita<sup>1</sup> (1. The Univ. of Tokyo (Japan))

2:20 PM - 2:40 PM JST | 5:20 AM - 5:40 AM UTC

[S6-03]

Impact of Substrate-Surface Oxidation Treatment and Post-Deposition Annealing on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (001) MOS Interfaces with ALD-Deposited Al<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub>

\*Atsushi Tamura<sup>1</sup>, Hayama Imaida<sup>1</sup>, Hiroyasu Maekawa<sup>2</sup>, Koji Kita<sup>1,2</sup> (1. Dept. of Advanced Materials Science, The Univ. of Tokyo (Japan), 2. Dept. of Materials Engineering, The Univ. of Tokyo (Japan))

2:40 PM - 3:10 PM JST | 5:40 AM - 6:10 AM UTC

[S6-04]

Exploration of new materials for meta-materials and power semiconductor applications

\*Kentaro Kaneko<sup>1</sup> (1. Ritsumeikan Univ. (Japan))

Program IWDTF2025

Power Device & Processes | Electron device, process, and characterization

**m** Fri. Nov 7, 2025 3:25 PM - 4:25 PM JST | Fri. Nov 7, 2025 6:25 AM - 7:25 AM UTC **m** 5F-Meeting Room

## [S7] Power Device & Processes (2)

Chair: Motoyuki Sato (Tokyo Electron), Toshinori Numata (Toyota Technological Institute)

3:25 PM - 3:55 PM JST | 6:25 AM - 6:55 AM UTC

[S7-01]

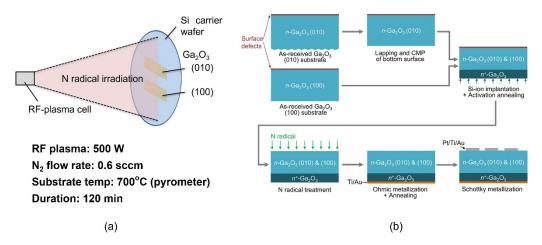

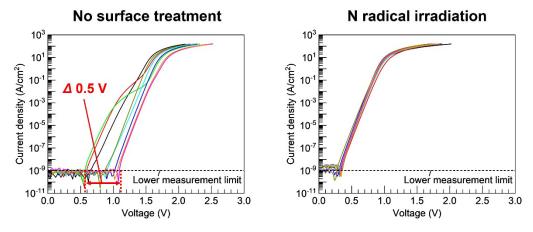

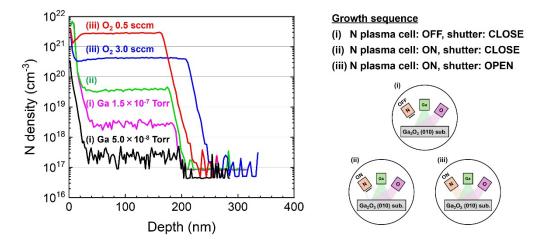

### Effects of Nitrogen Doping on Electrical Properties of Ga<sub>2</sub>O<sub>3</sub>

\*Masataka Higashiwaki<sup>1,2</sup>, Jin Inajima<sup>1</sup>, Tomoki Uehara<sup>1</sup>, Yusuke Teramura<sup>1</sup>, Kohki Tsujimoto<sup>1</sup>, Satoko Honda<sup>1</sup>, Zhenwei Wang<sup>2</sup> (1. Osaka Metropolitan Univ. (Japan), 2. National Institute of Information and Communications Technology (Japan))

3:55 PM - 4:25 PM JST | 6:55 AM - 7:25 AM UTC

[S7-02]

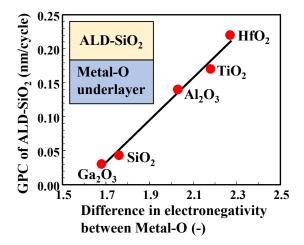

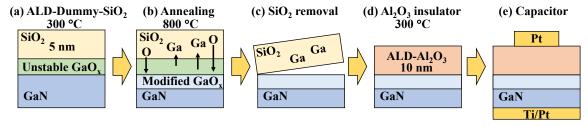

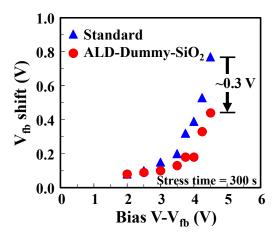

### Unique techniques of ALD for semiconductor devices

\*TOSHIHIDE NABATAME<sup>1</sup> (1. National Institute for Materials Science (Japan))

Closing

**ਛ** Fri. Nov 7, 2025 4:25 PM - 4:50 PM JST | Fri. Nov 7, 2025 7:25 AM - 7:50 AM UTC **☎** 5F-Meeting Room

## [CS] Closing

Chair:Masao Inoue(Renesas Electronics), Mitsuru Sometani(National Institute of Advanced Industrial Science and Technology (AIST))

Session IWDTF2025

Thermal Oxidation Mechanism & 2D Materials | Simulation & Characterization

**➡** Fri. Nov 7, 2025 9:00 AM - 10:40 AM JST | Fri. Nov 7, 2025 12:00 AM - 1:40 AM UTC **➡** 5F-Meeting Room

## [S5] Thermal Oxidation Mechanism & 2D Materials

Chair:Takanobu Watanabe(Waseda University), Koji Kita(The University of Tokyo)

9:00 AM - 9:20 AM JST | 12:00 AM - 12:20 AM UTC [S5-01]

First-principles study of excess Si transport in Si oxide on Si substrate using two-layer-oxide model for thermally oxidized interface

\*Hiroyuki Kageshima<sup>1</sup>, Insung Seo<sup>1</sup>, Toru Akiyama<sup>2</sup>, Kenji Shiraishi<sup>3</sup> (1. Shimane University (Japan), 2. Mie University (Japan), 3. Tohoku University (Japan))

9:20 AM - 9:40 AM JST | 12:20 AM - 12:40 AM UTC [S5-02]

Oxygen Pressure Dependence of Linear-Parabolic Growth Retardation on Si(111)

\*Hengyu Wen<sup>1</sup>, Yasutaka Tsuda<sup>2</sup>, Yuki Okabe<sup>1</sup>, Akitaka Yoshigoe<sup>2</sup>, Jiayi Tang<sup>3</sup>, Yuji Takakuwa<sup>4</sup>, Shuichi Ogawa<sup>1</sup> (1. Nihon University (Japan), 2. JAEA (Japan), 3. JASRI (Japan), 4. Tohoku University (Japan))

9:40 AM - 10:00 AM JST | 12:40 AM - 1:00 AM UTC [S5-03]

Cooperation Mechanism between Single- and Double-Step Oxidation Reaction Loops during Dry Oxidation on p-Si(001) and n-Si(001) Surfaces

\*Yuki Okabe<sup>1</sup>, Yasutaka Tsuda<sup>2</sup>, Hengyu Wen<sup>1</sup>, Akitaka Yoshigoe<sup>2</sup>, Yuji Takakuwa<sup>3</sup>, Shuichi Ogawa<sup>1</sup> (1. Nihon University (Japan), 2. JAEA (Japan), 3. Tohoku University (Japan))

10:00 AM - 10:20 AM JST | 1:00 AM - 1:20 AM UTC [S5-04]

Segregation induced formation of two-dimensional like GeSn ultra-thin crystal

\*Shigehisa Shibayama<sup>1</sup>, Taiga Mtasumoto<sup>1</sup>, Akio Ohta<sup>2</sup>, Ryo Yokogawa<sup>3,4,5</sup>, Mitsuo Sakashita<sup>1</sup>, Masashi Kurosawa<sup>1</sup>, Osamu Nakatsuka<sup>1,6</sup> (1. Grad. Sch. of Eng., Nagoya Univ. (Japan), 2. Faculty of Sci., Fukuoka Univ. (Japan), 3. RISE, Hiroshima Univ. (Japan), 4. Grad. Sch. of Adv. Sci. and Eng., Hiroshima Univ. (Japan), 5. MREL (Japan), 6. IMaSS, Nagoya Univ. (Japan))

10:20 AM - 10:40 AM JST | 1:20 AM - 1:40 AM UTC [S5-05]

Role of Annealing Atmosphere Towards Stoichiometry and Chemical Integrity of Solution-Processed  ${\rm MoS}_2$  Thin films

\*Md Iftekharul Alam<sup>1</sup>, Shungo Nagata<sup>1</sup>, Jaehyo Jang<sup>2</sup>, Hayato Kosaka<sup>1</sup>, Naoki Matsunaga<sup>2</sup>, Yoshiteru Amemiya<sup>1</sup>, Ryo Yokogawa<sup>1</sup>, Hitoshi Wakabayashi<sup>2</sup>, Akinobu Teramoto<sup>1</sup> (1. Hiroshima Uiversity (Japan), 2. Institute of Science Tokyo (Japan))

S5-01 IWDTF2025

## First-principles study of excess Si transport in Si oxide on Si substrate using twolayer-oxide model for thermally oxidized interface

Hiroyuki Kageshima<sup>1</sup>, Insung Seo<sup>1</sup>, Toru Akiyama<sup>2</sup>, and Kenji Shiraishi<sup>3</sup>

<sup>1</sup>Shimane Univ., <sup>2</sup>Mie Univ., <sup>3</sup>Tohoku Univ.

<sup>1</sup>1060 Nishi-Kawatsucho, Matsue, Shimane 690-8504, Japan

Email: kageshima@shimane-u.ac.jp

#### 1. Introduction

Silicon (Si) metal-oxide-semiconductor (MOS) interfaces are critical not only in conventional MOS field effect transistors (MOSFETs) but also in emerging Si-based devices, such as electron fluid effect devices and qubits for Si quantum computers. A detailed understanding of these interfaces is essential for further advancements in device performance. We have highlighted the significance of excess Si transport from the Si interface into the oxide layer during the thermal oxidation of Si. This excess Si transport is key to consistently explaining both the initially enhanced oxidation and the pattern-dependent oxidation. Furthermore, it provides a framework for understanding why the thickness and density of the interfacial high-density layer remain constant throughout the oxidation process, which is an essential factor in controlling interfacial reactions. We have investigated this excess Si transport by proposing that it occurs via SiO interstitials (I<sub>SiO</sub>) [1-4]. In this study, we investigate excess Si transport at the thermal Si-oxide/Si interface from a broader perspective, using a two-layer-oxide model with cristobalite/quartz/Si interface, which effectively captures key characteristics of actual thermal oxide interfaces.

#### 2. Method and Model

We investigate  $I_{SiO}$  transport paths in newly developed a two-layer-oxide model using first-principles calculations with PHASE0 [5]. The method details are similar to those in our previous studies [1-4]. The energy landscape is calculated based on the climbing-image nudged-elastic-band (CI-NEB) method.

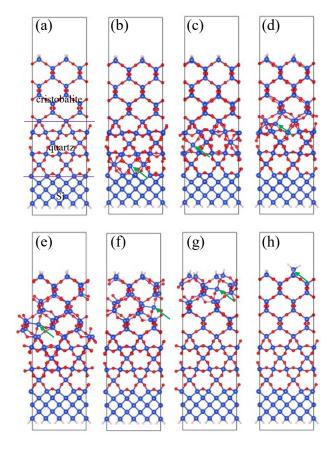

The two-layer-oxide model with cristobalite/quartz/Si interface is constructed by stacking a cristobalite layer on top of our previously established quartz/Si interface model (Fig.1(a)). The model is simple yet sufficiently accurate to capture the averaged structural properties of the thermal Si oxide interface.

We have been using the quartz interface model because quartz can be formed by oxidizing Si-Si and then performing appropriate Si release for strain relaxation [6]. The quartz interface model was used to imitate this high density after the Si release as excess Si. We have shown that the quartz interface model must also be used to reproduce the barrier heights obtained experimentally for interfacial reaction process between oxygen (O<sub>2</sub>) and Si [7]. The quartz layer at the interface must further keep a constant thickness regardless of the oxide thickness to reproduce the Deal-Grove theory. On the other hand, we have also shown that the cristobalite model must be used to reproduce the experimental barrier height for O<sub>2</sub> diffusion in the oxide film [8]. The density of the upper oxide layer is considered to be 2.2 g/cm<sup>3</sup> from various experiments, which is certainly consistent with the density of cristobalite. In other words, the Si thermal oxide film is considered to be

Fig. 1 (a) Atomic structure of the two-layer-oxide model with cristobalite/quartz/Si interface. And those of the metastable structures of  $I_{\rm SiO}$  on the transport path: the (b) 0th, (c) 126th, (d) 186th, (e) 210th, (f) 234th, (g) 258th, and (h) 288th images corresponding to the horizontal axis in Fig. 2, respectively. Red and blue spheres indicate O and Si atoms, respectively. Green arrows indicate excess Si of  $I_{\rm SiO}$ .

© IWDTF2025 - S5-01 -

\$5-01 IWDTF2025

composed of at least two layers of oxide: a dense quartz-like interfacial layer and a cristobalite-like upper oxide layer.

Based on these considerations, we have successfully developed a model of the Si thermal oxide film interface. There are no dangling bonds anywhere and a seamless network of only Si-Si and Si-O-Si bonds without defects.

#### 3. Results and Discussion

We have placed an  $I_{\text{SiO}}$  within the model, and successfully identified the transport path of the exess Si from the interface to the surface. The identified energy landscape is shown in Fig. 2, and some of metastable structures on the path are shown in Figs. 1(b)-(h). The indices of images correspond to the horizontal axis of Fig. 2.

The  $I_{\text{SiO}}$  is less stable by 1.12 eV at the 66th image in the middle of quartz layer than

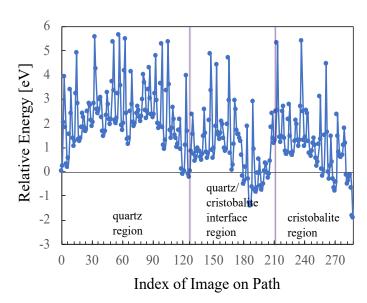

Fig. 2 Energy landscape for the transport path of  $I_{\text{SiO}}$  from the interface to the surface of the oxide in the two-layer-oxide model. The energies are measured from the 0th image.

at the initial 0th image at the quartz/Si interface, and is also less stable by 0.70 eV at the 222nd image in the middle of cristobalite layer. However, it is slightly more stable by 0.23 eV at the 126th image at the surface of quartz layer, and even much more stable by 1.44 eV at the 186th image at the cristobalite/quartz interface. It further becomes significantly more stable by 1.92 eV at the final 288th image at the cristobalite surface. Notably, this surface stabilization is about 0.5 eV greater than that calculated at the quartz surface of the quartz/Si interface model in our previous study [4]. These results suggest that the excess Si can pile up at the cristobalite/quartz interface as well as at the cristobalite surface.

For the excess Si transport, the maximum barrier height through the quartz region (0th to 126th) is 5.61 eV, that through the cristobalite/quartz interface region (126th to 210th) is 4.84 eV, and that through the cristobalite region (210th to 288th) is 5.38 eV. Therefore, the overall barrier height is 5.61 eV. This value is larger than that of 4.55 eV calculated for the quartz/Si interface model in our previous study [4]. Because the surface is covered by the cristobalite layer, it seems that the quartz layer becomes less flexible and that the barrier height increases. However, this overall barrier height is still reasonably consistent with experimental results ranging from approximately 4 to 6 eV [9]. These results suggest that the excess Si can surely transport in the oxide from the interface to the surface during the Si thermal oxidation process.

#### 4. Conclusions

We have constructed a two-layer-oxide model for the thermal Si oxide/Si interface, and successfully identified the excess Si transport path and its energy landscape in the oxide from the interface to the surface. We found that excess Si can pile up at the quartz/cristobalite interface as well as the cristobalite surface. We also found that the maximum barrier height is reasonably consistent with experiments.

#### Acknowledgements

A part of this study has been supported by KAKENHI (22K18294). A part of calculations is performed in the Super-computer Center of ISSP, University of Tokyo. Atomic structures are depicted with using VESTA.

#### References

- [1] H. Kageshima, et al., Mater. Sci. Semicond. Process. **162**, 107527 (2023).

- [2] H. Kageshima, et al., Jpn. J. Appl. Phys. **63**, 04SP08 (2024).

- [3] H. Kageshima, et al., J. Phys. Soc. Jpn. 94, 074707 (2025).

- [4] H. Kageshima, et al., e-J. Surf. Sci. Nanotechnol. 23, advanced publication (2025).

- [5] https://azuma.nims.go.jp

- [6] H. Kageshima, et al., Phys. Rev. Lett. 81, 5936 (1998).

- [7] T. Akiyama, et al., Phys. Rev. B 77, 115356 (2008).

- [8] T. Akiyama, et al., Thin Solid Films **508**, 3111 (2006).

- [9] M. Uematsu, et al., Appl. Phys. Lett. **84**, 876 (2004).

© IWDTF2025 - \$5-01 -

\$5-02 IWDTF2025

## Oxygen Pressure Dependence of Linear-Parabolic Growth Retardation on Si(111)

Hengyu Wen <sup>1</sup>, Yasutaka Tsuda <sup>2</sup>, Yuki Okabe <sup>1</sup>, Akitaka Yoshigoe <sup>2</sup>, Jiayi Tang<sup>3</sup>,

Yuji Takakuwa<sup>4</sup>, and Shuichi Ogawa<sup>1</sup>

<sup>1</sup>Nihon Univ., <sup>2</sup>JAEA, <sup>3</sup>JASRI, <sup>4</sup>Tohoku Univ.

<sup>1</sup>1-2-1 Izumi-cho, Narashino, Chiba 275-8575, Japan

Email: ciko25021@g.nihon-u.ac.jp / Phone: +81-47-474-2383

#### 1. Introduction

The Si dry oxidation process is well described by the linear-parabolic growth model, except for the initial decrease in the oxidation rate below 20-40 nm [1]. Oxidation-induced vacancies act as O<sub>2</sub> dissociative adsorption sites during the initial decrease in oxidation rate [2-4]. According to this concept, single- and double-step oxidation reaction loops (Loops A and B) proceed cooperatively, and the reaction order of Loops A and B is first-order. Regarding the thickness of the SiO<sub>2</sub> layer, X<sub>O</sub>, the linear-parabolic growth model is represented as follows:

$$X_0^2 + AX_0 = B(t + \tau)$$

(1)

In thin  $X_0$ , eq. (1) is approximated by eq. (2).

$X_0 \cong \frac{B}{A}(t + \tau)$  (2)

This means that the interfacial reaction is of zero order. This study investigates the origin of  $0^{\text{th}}$ -order SiO<sub>2</sub> growth from the perspective of linear-parabolic growth retardation by observing  $X_{\text{O}}$  and  $\Delta BB$  as a function of  $P_{\text{O2}}$  during dry oxidation on p-Si(111) surfaces with real-time XPS at SPring-8.

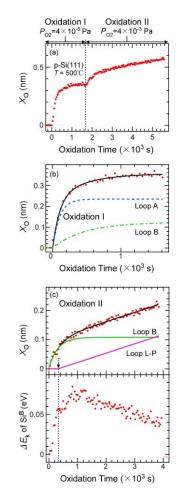

Fig. 1 Loops A/B & L-P model for p-Si(111) surface.

#### 2. Loops A/B & L-P model

Figure 1 shows the Loops A/B and L-P model,

in which the first-order reactions of Loops A and B are combined with the zero-order reaction of Loop L-P. In this model,  $X_0$  is represented as follows:  $A_A$  and  $A_B$  are the saturation levels, and  $k_A$  and  $k_B$  are the reaction coefficients for Loops A and B, respectively. A and B are the same as in Ref. [1]. For the retardation time of Loop L-P,  $(t - \tau)$  is used in Eq. (3), which is different from Eq. (1).

$$Xo = A_A(1 - e^{-k_A t}) + A_B(1 - e^{-k_B t}) + \frac{1}{2} \left[ -A + \sqrt{A^2 + 4B(t - \tau)} \right]$$

(3)

The generation of point defects during surface oxidation marks the start of Loops A/B. The branching ratio between these loops is governed by  $\gamma_A$ , leading to the appearance of  $2(P_{b0} + P_{b1})^+$ .  $2(P_{b0} + P_{b1})^+$  is the intermediate state of Loop B and the start of Loop L-P after minority carrier trapping. Oxidation-induced stress (about 8-11 gigapascals) and heat of adsorption (8-11 electronvolts) are responsible for the defect generation. There's a point defect (a missing atom) at the Si side in Loops A/B, and Si-O breaking (Si<sub>3</sub> = Si · · · O-Si = O<sub>3</sub>) at the SiO<sub>2</sub> side in Loop L-P. Si<sub>3</sub> = Si · can adsorb oxygen (O<sub>2</sub>) and act as a  $P_{b0}$  center. However, for the vacancy site to be active, it needs to rearrange minority carriers.

#### 3. Results and Discussion

As shown in Fig. 1(a), increasing  $P_{\rm O2}$  has a big effect on enhancing silicon dioxide (SiO<sub>2</sub>) growth. In the oxidation of Si(111) at  $4\times10^{-5}$  Pa, the surface oxidation process is best described by eq. (3) for only Loops A/B. The contribution from Loop L-P is not needed at all during the 1600-second time period examined, as shown in Fig. 1(b). Loop A takes about 2000 seconds, and SiO<sub>2</sub> growth continues through Loop B even at the end of

© IWDTF2025 - S5-02 -

\$5-02 IWDTF2025

Oxidation I. As shown in Fig. 1(c), Oxidation II requires Loop L-P with an offset  $\tau$  of 325 seconds, in addition to Loop B.  $dX_0/dt$  in Loop B increases 42 times, from  $8.1 \times 10^{-6}$  to  $3.4 \times 10^{-4}$  nm/s, upon an increase in  $P_{02}$  from  $4 \times 10^{-5}$  to  $4 \times 10^{-3}$  Pa. It is important to note that  $\tau$  in  $X_0$  is in good agreement with  $\Delta E_k$  of Si<sup>B</sup>, which quickly saturates and then increases gradually. Loop B is linked to a reduction in downward BB for p-Si, meaning a decrease in V<sup>+</sup>. On the other hand, downward BB changes very gradually during Loop L-P. The latter supports the idea shown in Fig. 1. This figure shows that having extra minority carrier recombination is not necessary for the active site of Si<sub>3</sub>  $\equiv$  Si • for O<sub>2</sub> dissociation in Loop L-P. However, majority carrier trapping (V<sup>0</sup> + h<sup>+</sup>  $\rightarrow$  V<sup>+</sup>) plays an important role in activating the vacancy in Loops A/B.

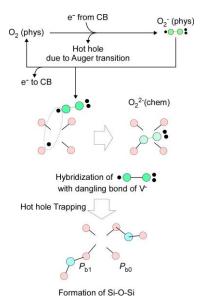

When maintaining  $P_{O2}$  at  $4\times10^{-5}$  Pa,  $\tau$  is extended to 4600 s (1600 s + 3000 s). This shows that L-P growth retardation is shortened from 3000 to 325 seconds by increasing  $P_{02}$  100 times at 500°C. When cooling down to room temperature at  $4\times10^{-5}$  Pa,  $\tau$  is stretched to 6915s (1600s + 5315s). As a result,  $\tau$  is shortened by raising the temperature and increasing  $P_{O2}$ . In Fig. 1,  $2(P_{b0} + P_{b1}) - O_2^2$  (chem), paul-5p, is the start of Loop L-P. paul-5p doesn't need minority carrier trapping for electric neutrality. However, hot hole trapping at the bonding orbital  $\sigma_g$ of  $O_2^{2-}$  (chem) makes it possible to dissociate  $O_2^{2-}$  (chem). The number of hot holes increases with rising temperature, according to the shortening of  $\tau$ . On the other hand, hot holes are created through an Auger transition, which is associated with electron tunneling from Si CB to  $O_2(phys)$ , resulting in  $O_2(phys)$ . When  $2(P_{b0} + P_{b1})$  and  $O_2(phys)$ (phys) hybridize, the result is the formation of paul-5p. Otherwise, electrons might tunnel from O<sub>2</sub> (phys) to Si CB. The process of hopping at the interface causes the repetition of  $O_2(phys) \rightleftarrows O_2(phys)$ . This leads to the accumulation of enough hot holes. As  $P_{02}$  increases, the hot hole accumulation becomes effective. This allows us to shorten  $\tau$ , as we have observed. Additionally, Loop B without O<sub>2</sub> #2 makes the density of  $2(P_{b0} + P_{b1})$  much smaller compared to that of  $2(P_{b0} + P_{b1})^{-1}$ in Loop B. This reduces the frequency of the formation of paul-5p a

Once the Si-O bond is broken due to heat of adsorption (Si<sub>3</sub>  $\equiv$  Si ·

+ • O-Si  $\equiv$  O<sub>3</sub>), an active site such as a  $P_{b0}$  center appears. This process is called "Si-O breaking", making it possible to start a process called "Loop L-P." The Si-O breaking number is more than one because of the sufficient heat of adsorption. The reason is that four Si-O bonds are formed by O<sub>2</sub> dissociation at the  $P_{b0}$  center and one Si-O is added due to rebonding between Si<sub>3</sub> $\equiv$ Si · and · O-Si $\equiv$ O<sub>3</sub>. This means that Loop L-P is not limited by the number of Si<sub>3</sub> $\equiv$ Si · sites. Instead, it is governed by the supply of O<sub>2</sub>-(phys). This suggests that the 0<sup>th</sup>-order reaction of Loop L-P is governed by O<sub>2</sub>-(phys). In Fig. 2,  $\tau$ -1 and B/A show a nonlinear dependence on  $P_{O2}$ . Both of them are likely worried about the separation of O<sub>2</sub><sup>2</sup>-(chem) because of hot hole trapping.

#### 4. Conclusions

The L-P growth retardation revealed the following: The origin of Loop L-P is  $2(P_{b0} + P_{b1})$  in Loop B; The frequency of appearance of *paul*-5p is reduced by excess minority carrier recombination without O<sub>2</sub>; The dissociation of *paul*-5p is governed by hot hole trapping; and Si-O breaking (Si<sub>3</sub>  $\equiv$  Si  $\cdot$  +  $\cdot$  O-Si  $\equiv$  O<sub>3</sub>) acts as an O<sub>2</sub> dissociation site.

#### References

- [1] H.M. Massoud et al., J. Electrochem. Soc. 132, 2685 (1985).

- [2] S. Ogawa et al., Jpn. J. Appl. Phys. **59**, SM0801 (2020).

- [3] Y. Tsuda et al., J. Chem. Phys. 157, 234705 (2022).

- [4] Y. Tsuda et al., e-J. Surf. Sci. Nanotech. 21, 30 (2023).

Fig. 2 (a) Changes of  $X_0$  upon  $P_{O2}$  increase between Oxidation I and II. Curve-fitting analysis of  $X_0$ : (b) Oxidation I and (c) II. (d)  $\Delta BB$  obtained in Oxidation II.

Fig. 3  $P_{O2}$  dependence of (a)  $\tau^1$  and (b) B/A for Loop L-P.

© IWDTF2025 - S5-02 -

S5-03 IWDTF2025

## Cooperation Mechanism between Single- and Double-Step Oxidation Reaction Loops during Dry Oxidation on p-Si(001) and n-Si(001) Surfaces

Yuki Okabe<sup>1</sup>, Yasutaka Tsuda<sup>2</sup>, Hengyu Wen<sup>1</sup>, Akitaka Yoshigoe<sup>2</sup>, Yuji Takakuwa<sup>3</sup>, and Shuichi Ogawa<sup>1</sup>

<sup>1</sup>Nihon Univ., <sup>2</sup>JAEA, <sup>3</sup>Tohoku Univ.

<sup>1</sup>1-2-1 Izumi-cho, Narashino, Chiba 275-8575, Japan

Email: ciyu25010@g.nihon-u.ac.jp / Phone: +81-47-474-2383

#### 1. Introduction

The initial oxidation rate reduction in Si dry oxidation was interpreted by a unified Si oxidation reaction model mediated by oxidation-induced defect generation (Loops A/B & L-P model). In this model, singleand double-step oxidation reaction loops A and B are cooperated. Furthermore, majority and minority carrier trapping occur at vacancy-derived levels [2], and trappingmediated adsorption of O2 proceeds at vacancies and  $P_b$  centers [3]. In this study, the cooperative mechanism between Loops A and B was investigated by comparing  $SiO_2$  thickness,  $X_0$ , between p-Si(001) and n-Si(001) surfaces. This was observed in situ as a function of temperature by XPS at SPring-8.

# SisVOX O<sub>2</sub>(chem) Loop A w/o O<sub>2</sub> k<sub>mCT</sub> O<sub>2</sub>(chem paul-4n Loop B w/ O-0<sub>b1</sub>)-- O<sub>2</sub>(chem) paul-5n

Fig. 1 Unified Si oxidation reaction model mediated by oxidationinduced point defect generation.

#### 2. Loops A/B & L-P model

As illustrated in Fig. 1, the initiation of Loops A and B is facilitated by O<sub>2</sub>

dissociation at the dangling bonds of the dimer. In the absence of trapping minority carrier, the dissociation of paul-3n occurs spontaneously, resulting in the emergence of  $2(P_{b0} + P_{b1})$  in the intermediate state of Loop B. Conversely, paul-3n leads to SiO<sub>2</sub> growth, thereby enabling the progression of Loop A. The branching between Loops A and B is governed by  $\gamma_A$ . As demonstrated in reference 4, the variable  $2(P_{b0} + P_{b1})$  is associated with linear-parabolic growth (Loop L-P). In the Loops A/B & L-P model,  $X_0$  is represented analytically as follows, where  $A_A$  and  $A_B$ , and  $k_A$  and  $k_B$ , represent the saturation level and reaction coefficient in Loops A and B, respectively. It is noteworthy that A and B in Loop L-P are equivalent to those in Ref. [4].

$$X_0 = A_{\rm A}(1 - e^{-k_{\rm A}t}) + A_{\rm B}(1 - e^{-k_{\rm B}t}) + \frac{1}{2} \left[ -A + \sqrt{A^2 + 4B(t - \tau)} \right] \tag{1}$$

Since Loop L-P has an offset as shown in Fig. 2, the initial values of  $dX_0/dt$  upon O<sub>2</sub> introduction are given by  $A_A \cdot k_A$  and  $A_B \cdot k_B$  for Loops A and B, respectively. They have the following relation with  $\gamma_A$  and  $O_2$ adsorption coefficients of  $k_{\rm OX}$  in Loop A and  $k_{\rm OX1}$  and  $k_{\rm OX2}$  in Loop B [1].  $R = \frac{k_A \cdot A_A}{k_B \cdot A_B} = \frac{k_{OX}}{k_{OX1} \cdot k_{OX2}} \cdot \frac{\gamma_A}{(1 - \gamma_A)}$ (2)

R is obtained by fitting  $X_{\rm O}$  with eq. (1) and  $k_{\rm OX}$  is the same as  $k_{\rm XO1}$  because of  $O_2$  adsorption at V for both the

$$R = \frac{k_A \cdot A_A}{k_B \cdot A_B} = \frac{k_{OX}}{k_{OY1} \cdot k_{OY2}} \cdot \frac{\gamma_A}{(1 - \gamma_A)} \tag{2}$$

cases. As a result, the cooperation mechanism between Loops A and B is considered with  $\gamma_A$  estimated with eq. (3).

$$\gamma_A = \frac{R \cdot k_{OX2}}{1 + R \cdot k_{OX2}} \tag{3}$$

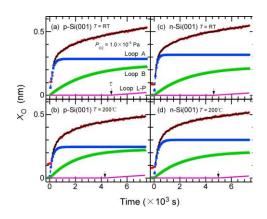

#### 3. Results and Discussion

As illustrated in Fig. 2, the offset of Loop L-P ranges from 4300 to 5100 seconds, and the slope B/A is negligible. It is evident that Loops A and B demonstrate a substantial discrepancy between p- and n-Si(001) surfaces, as well as between RT and 200°C. It has been observed that Loop A increases rapidly and reaches a state of saturation within the range of 1000 to 2000 seconds. Conversely, Loop B demonstrates a more gradual

© IWDTF2025 - S5-03 - \$5-03 IWDTF2025

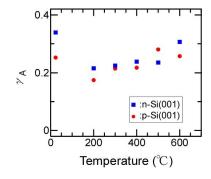

increase in its response. These observations imply that the relationship between Loops A and B is contingent on the conduction type and the ambient temperature. The calculation of  $\gamma_A$  is performed using equation (3), as illustrated in Fig. 3, based on the fitting parameters. At RT,  $\gamma_A$  demonstrates a substantial discrepancy: The values 0.252 and 0.339 were obtained for p- and n-Si(001), respectively. When the temperature is increased to 200°C,  $\gamma_A$  decreases down to approximately 0.2 for both surfaces and then increases gradually with temperature. The observed dependence indicates that  $\gamma_A$  is governed by two distinct factors.

The majority carrier trapping process  $(V^0 + e^- \rightarrow V^-)$  for n-Si(001) yields a dangling bond, which subsequently undergoes hybridization with O<sub>2</sub>-(phys) ( • O-O:), thereby forming V-O<sub>2</sub><sup>2</sup>-(chem), as depicted in Fig. 4. The formation of paul-3n requires the trapping of minority carrier h<sup>+</sup> at V<sup>-</sup> for SiO<sub>2</sub> growth, while maintaining electrical neutrality. This is the primary factor of  $\gamma_A$ . The trapping of holes (h<sup>+</sup>) is promoted via the Coulomb interaction by O<sub>2</sub><sup>2</sup>-(chem). The minority carrier trapping of electrons (e<sup>-</sup>) at V<sup>+</sup> for p-Si(001) is disturbed by  $O_2^{2-}$  (chem). This phenomenon elucidates the observed disparity in the values of  $\gamma_A$  (p-Si) and  $\gamma_A$ (n-Si) at room temperature (RT). It is noteworthy that dissociation of O<sub>2</sub><sup>2</sup>-(chem) is achieved by hot hole trapping at the bonding orbital  $\sigma_g$  with  $E_B = 5.1$  eV. Electron tunneling from Si CB to O<sub>2</sub>(phys) results in the formation of O<sub>2</sub>-(phys) with a single bond, accompanied by the production of hot holes with a maximum energy of ~7 eV through the Auger transition. The occurrence of electron tunneling from O<sub>2</sub> (phys) to Si is attributed to the energetic instability of O₂-(phys). The repetition of O₂(phys) ≥ O₂-(phys) during hopping on the surface supplies a number of hot holes, which are responsible for the dissociation of  $O_2^{2-}$  (chem). This is the second factor of  $\gamma_A$ . Given the prevalence of hot hole trapping in both p- and n-Si(001), it is anticipated that  $\gamma_A$  (p-Si) and  $\gamma_A$  (n-Si) will exhibit a high degree of similarity, as evidenced by the observations made at temperatures exceeding 200°C in Fig. 3. As the temperature rises, the transition of oxygen molecules between O<sub>2</sub>(phys) and O<sub>2</sub> (phys), known as "hopping," becomes increasingly prevalent. This phenomenon leads to the distribution of hot holes, which are excess energy states in the material, extending beyond the vicinity of V-O<sub>2</sub><sup>2</sup>-(chem) and V+O<sub>2</sub><sup>2</sup>-(chem). Conversely, the vibration and rotation of O<sub>2</sub>-(chem) around V become effective in collecting hot holes due to the Coulomb force. Consequently, both  $\gamma_A$  (p-Si) and  $\gamma_A$  (n-Si) exhibit an increase in their values with increasing temperatures above 200°C.

#### 4. Conclusions

The cooperative process between Loops A and B is facilitated by  $\gamma_A$ , which is governed by minority carrier and hot hole trapping at V<sup>-</sup>-O<sub>2</sub><sup>2</sup>-(chem) and V<sup>+</sup>-O<sub>2</sub><sup>2</sup>-(chem). The minority carrier trapping at V<sup>-</sup> and V<sup>+</sup> for charge neutrality is the rate-limited step because of insufficient thermal excitation at RT. The distribution of hot holes with temperatures above 200°C is characterized by its extensive nature. Consequently, the process of hot hole trapping at O<sub>2</sub><sup>2</sup>-(chem) for dissociation becomes predominant in  $\gamma_A$ .

#### References

- [1] S. Ogawa et al., Jpn. J. Appl. Phys. **59**, SM0801 (2020).

- [2] Y. Tsuda et al., J. Chem. Phys. 157, 234705 (2022).

- [3] Y. Tsuda et al., e-J. Surf. Sci. Nanotech. 21, 30 (2023).

- [4] B. E. Deal and A. S. Grove, J. Appl. Phys. **36**, 3770 (1965).

Fig. 2 Curve-fitting analysis of  $X_0$  with eq. (1): (a), (b) p-Si(001), and (c), (d) n-Si(001). Arrows indicate the offset of Loop L-P.

Fig. 3 Temperature dependence of  $\gamma_A$ .  $k_{OX2}$  is assumed to be 0.02.

Fig. 4 Trapping-mediated adsorption model of O<sub>2</sub> at V<sup>-</sup>.

\$5-04 IWDTF2025

## Segregation induced formation of two-dimensional like GeSn ultra-thin crystal

Shigehisa Shibayama<sup>1</sup>, Taiga Matsumoto<sup>1</sup>, Akio Ohta<sup>2</sup>, Ryo Yokogawa<sup>3,4,5</sup>, Mitsuo Sakashita<sup>1</sup>, Masashi Kurosawa<sup>1</sup>, and Osamu Nakatsuka<sup>1,6</sup>

<sup>1</sup>Grad. Sch. of Eng., Nagoya Univ., <sup>2</sup>Faculty of Sci., Fukuoka Univ., <sup>3</sup>RISE, Hiroshima Univ., <sup>4</sup>Grad. Sch. of Adv. Sci. and Eng., Hiroshima Univ., <sup>5</sup>MREL, <sup>6</sup>IMaSS, Nagoya Univ.

<sup>1</sup>Furo-cho, Chikusa-ku, Nagoya 464-8603, Japan Email: s-shibayama@nagoya-u.jp / Phone: +81-52-789-2762

#### 1. Introduction

Germanium-based two-dimensional materials such as germanene, and germanium nanosheet (Ge-NS) have attracted attention as channel materials for ultimately miniaturised nanosheet transistors because it has a higher electron mobility and a wider band gap rather than graphene [1,2]. Recently, we have focused on GeSn-NS because Sn incorporation into Ge-NS will achieve a higher electron mobility and a higher band gap than Ge-NS [1,3]. However, GeSn-NS fabrication has not been mostly addressed and achieved yet.

To realize the GeSn-NS formation, we go back to Ge-NS fabrication methods reported so far. Previously, three methods have been mainly addressed: (1) the epitaxial growth on metal surface [4,5], (2) vacuum annealing to germanane chemically synthesised from CaGe<sub>2</sub> [6–8], and (3) the segregation from metal/Ge(111) structure e.g., Ag/Ge(111) and Al/Ge(111) [9,10]. Among them, the segregation method using Al/Ge(111) structure has a great merit that the segregated ultra-thin Ge crystal is atmospherically stable because Al<sub>2</sub>O<sub>3</sub> cover layer is simulatneously formed on the segregated Ge [10]. However, whether a segregated ultra-thin Ge crystal has two-dimensional structure or not has been still under discussion.

In this study, we demonstrated the GeSn-NS fabrication by the segregation method using  $Al/Ge_{1-x}Sn_x(111)$  structure. Furthermore, we performed the detail analysis of the crystalline structure of the segregation layer. As a result, we clarified that a GeSn-NS was successfully formed as a segregation layer covered with an Al-oxide layer, and the GeSn-NS showed two-dimensional like structure not a diamond structure.

#### 2. Experimental Procedure

A 3 inch Ge(111) wafer was used as a substrate. We performed chemical cleaning and thermal annealing at 430 °C for 30 min under ultra-high vacuum condition. Then, a  $\sim$ 30-nm-thick Ge<sub>0.88</sub>Sn<sub>0.12</sub> epitaxial layer was grown on Ge(111) substrate at 100 °C by molecular beam epitaxy (MBE), and the sample was taken out from the MBE chamber. Next, surface native oxide of the Ge<sub>0.88</sub>Sn<sub>0.12</sub> epitaxial layer was removed by HF and HCl mixed solution. Subsequently, thermal cleaning was performed at 300 °C for 30 min under high vacuum condition and a 30-nm-thick Al layer was grown at 100 °C by the vacuum evaporation method in the same chamber. Finally, we performed the post deposition annealing (PDA) at 300 °C for 30 min in an N<sub>2</sub> atmosphere to induce the segreagtion.

#### 3. Results and Discussion

At first, we checked the epitaxial growth of Ge<sub>0.88</sub>Sn<sub>0.12</sub> and Al layers by X-ray diffraction, and the segregation of Ge and Sn atoms on the Al layer by X-ray photoelectron spectroscopy (*the results are not shown here*). So next, the crystalline structure of the segeregation layer was analyzed in details using hard-angle annular dark field (HAADF)- and bright-field (BF)-scanning transmission electron microscopy (STEM) observation in conjunction with energy dispsersive X-ray spectroscopy (EDX).

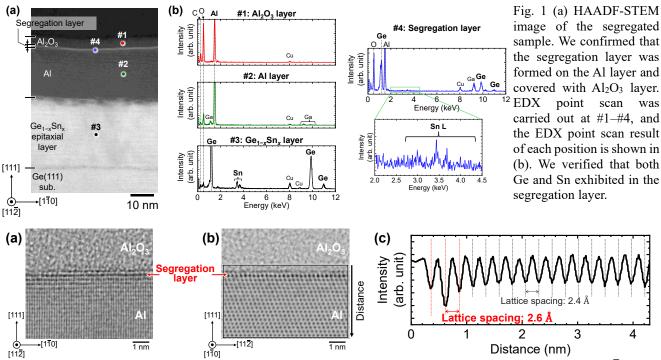

Figures 1(a) and 1(b) showed HAADF-STEM image and point-scan EDX results at four points #1—#4, respectively. From Fig. 1(a), we confirmed that some layered structure was formed. From the point-scan EDX results at #1—#4, each layer from the bottom to the upperside is clarified to correspond Ge<sub>0.88</sub>Sn<sub>0.12</sub> epitaxial layer, Al epitaxial layer, the segregation layer, and the Al<sub>2</sub>O<sub>3</sub> layer. Particularly, in the segregation layer, both Ge and Sn signals exhibited, meaning the GeSn segregation layer might be formed. The Sn composition of the GeSn segregation layer was estimated to 4.3—7.4%. Although, Al and O signals were also detected in the segregation layer, these signals could be originated from the Al<sub>2</sub>O<sub>3</sub> and Al layers because the segregation layer are ultimately thin comparing with the point-scan area.

Next, we discussed the detail crystalline structure of the segregation layer by higher resolution STEM observation. Figures 2(a) and 2(b) show BF-STEM images obtained from the incident direction of  $[11\bar{2}]$  and  $[1\bar{1}0]$ , respectively. We found that the GeSn segregation layer showed two-dimensional like structure with backling shape. However, the lattice spacing of the GeSn segregation layer in the [111] direction is larger than that of the Al layer. This is much more clearly observed in the projected line profiles as shown in Fig. 2(c), which was obtained from the black rectangle area shown in Fig. 2(b). The lattice spacing of the GeSn segregation layer was estimated to 2.6 Å, while that of the Al layer was 2.4 Å. Here, from other STEM results

© IWDTF2025 - S5-04 -

\$5-04 IWDTF2025

(not shown here), the lattice spacing of the Ge<sub>0.88</sub>Sn<sub>0.12</sub> epitaxial layer was estimated to 3.4 Å. Furthermore, the reported values of lattice spacing of germanene and Ge-NS formed on metal layer were ranged from 2.1–2.7 Å [11–16], infering the lattice spacing value of the GeSn segregation layer is well consistent with germanene and Ge-NS. This strongly suggests that the GeSn segregation layer has two-dimensional like structure rather than diamond structure.

#### 4. Conclusions

In this study, we addressed the GeSn-NS formation by the segregation method from the stacked structure of Al/Ge<sub>1-x</sub>Sn<sub>x</sub>(111) epitaxial layer. We demonstrated that the GeSn-segregation layer with Sn composition of 4.3-7.4% was formed on the Al layer and that was covered with the Al<sub>2</sub>O<sub>3</sub> layer. Furthermore, we firstly showed an evidence of the GeSn segregation layer showed two-dimensional like structure with a lattice spacing of 2.6 Å rather than diamond structure. We believe that this study opens a new door of the segregation method to develop various new materials of group-IV compound NS.

#### Acknowledgements

This work was partly supported by Canon Foundation, JSPS KAKENHI (23K17745, 22H01524, 21H01809), JST PRESTO (JPMJPR21B6), JST CREST (JPMJCR21C2).

#### References

- [1] L. Matthes et al., J. Phys.: Condens. Matter 25, 395305 (2013).

- [2] X. -S. Yet et al., RSC Adv. 4, 21216 (2014).

- [3] Y. Nakamura et al., Adv. Electron. Mater. 3, 1700143 (2017).

- [4] P. Vogt et al., Phys. Rev. Lett. 108, 155501 (2012).

- [5] T. Ogikubo et al., Adv. Mater. Interfaces 7, 1902132 (2020).

- [6] E. Bianco et al., ACS Nano 7, 4414 (2013).

- [7] M. Araidai et al., J. Appl. Phys. 128, 125301 (2020).

- [8] M. Itoh et al., Jpn. J. Appl. Phys. 61, SC1048 (2022).

- [9] M. Kurosawa et al., Jpn. J. Appl. Phys. 55, 08NB07 (2016).

- [10] M. Kobayashi et al., Jpn. J. Appl. Phys. 59, SGGK15 (2020).

- [11] Z. Qin et al., Adv. Mater. 29, 1606046 (2017).

- [12] Q. Tian et al., Phys. Rev. B 110, 125430 (2024).

- [13] K. Zhang et al., ACS Nano 17, 15687 (2023).

- [14] J. Yuhara et al., ACS Nano 12, 11632 (2018).

- [15] J. Yuhara et al., 2D Mater. 5, 036003 (2018).

- [16] D.M. Muzychenko et al., Mater. Today Phys. 14, 100241 (2020).

Fig. 2 High resolution BF-STEM images of the segregated sample obtained with the incident direction of (a) [11 $\overline{2}$ ] and (b) [1 $\overline{1}$ 0]. The projected line profile was obtained from the black rectangle area in Fig. 2(b) with the direction from Al<sub>2</sub>O<sub>3</sub> to Al, which is shown by the black arrow. The obtained profile was shown in (c). We found that the lattice spacing of the segregation layer is clearly different with the Al layer.

© IWDTF2025 - S5-04 -

\$5-05 IWDTF2025

# Role of Annealing Atmosphere Towards Stoichiometry and Chemical Integrity of Solution-Processed MoS<sub>2</sub> Thin Films

Md Iftekharul Alam<sup>1</sup>, Shungo Nagata<sup>1</sup>, Jaehyo Jang<sup>2</sup>, Hayato Kosaka<sup>1</sup>, Naoki Matsunaga<sup>2</sup>, Yoshiteru Amemiya<sup>1</sup>, Ryo Yokogawa<sup>1</sup>, Hitoshi Wakabayashi<sup>1</sup>, Akinobu Teramoto<sup>1</sup>,

<sup>1</sup>Hiroshima Univ., <sup>2</sup>Institute of Science Tokyo

<sup>1</sup>1-3-2 Kagamiyama, Higashihiroshima, Hiroshima 739-0046

Email: iftekhar@hiroshima-u.ac.jp / Phone: +81-82-424-6265

#### 1. Introduction

Among various approaches, solution process is one of the quickest and simplest methods to produce MoS<sub>2</sub> thin films, compared to other techniques such as chemical vapor deposition (CVD), atomic layer deposition (ALD), and mechanical exfoliation [1-3]. However, their stoichiometry and chemical integrity are typically affected by sulfur vacancies (V<sub>s</sub>) that serve as reactive sites for oxygen incorporation and cause degradation in device performance [4]. Annealing in sulfur vapor (S-vapor) represents a promising technique toward the restoration of stoichiometry through sulfur replenishing and concurrent oxidation suppression. Herein, we demonstrate the solution-based synthesis of MoS<sub>2</sub> films on Si<sub>3</sub>N<sub>4</sub> surfaces with various precursor concentrations (5, 12, 16, 20, 25, and 30 mM) followed by annealing in argon (Ar) and sulfur vapor (S-vapor) at 700 °C. S-vapor annealed films achieved a near-ideal S/Mo ratio (~2:1) with significantly lower oxidation than Arannealed films, indicating the strong influence of annealing atmosphere on the stability of MoS<sub>2</sub>.

#### 2. Experimental Procedure

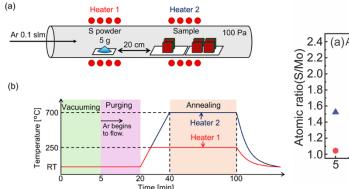

Molybdenum disulfide (MoS<sub>2</sub>) films were prepared from a precursor solution via a single-step annealing in Ar and S-vapor atmospheres. The precursor solution was obtained by dissolving ammonium tetrathiomolybdate [(NH<sub>4</sub>) <sub>2</sub>MoS<sub>4</sub>, 99.999%, Sigma Aldrich] in a solvent mixture of dimethylformamide (DMF), isopropanol (IPA), and ethanolamine with the 3:5:3 (v/v) ratio. The solution was stirred for 2 h, and spin-coated on clean Si<sub>3</sub>N<sub>4</sub> surfaces at 500 rpm for 10 s and 3000 rpm for 30 s. The Si<sub>3</sub>N<sub>4</sub> surfaces were treated with 0.5% HF for 60s followed by rinse with DI water. The films were pre-annealed at 180 °C for 30 min and annealed at 700 °C for 1 h under 1 slm Ar flow using a lamp annealing system. S-vapor annealing procedures are demonstrated in Fig.1. The fabricated MoS<sub>2</sub> films were characterized using transmission electron microscopy (TEM), Raman spectroscopy, x-ray photoelectron spectroscopy (XPS) and thermal desorption spectroscopy (TDS) respectively.

#### 3. Results and Discussion

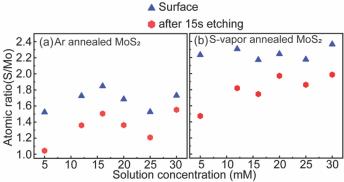

To assess the stoichiometry and sulfur vacancy ( $V_s$ ) of the MoS<sub>2</sub> films, X-ray photoelectron spectroscopy (XPS) measurements were performed on both the surface and after 15 s etching, as illustrated in Fig. 2. At 5 mM, both films show sulfur deficiency (S/Mo ~2:1), but Ar-annealed films (Fig. 2a) remain sub-stoichiometric across all concentrations. In contrast, S-vapor annealed films (Fig. 2b) approach the ideal 2:1 ratio with increasing concentration and achieve homogeneous stoichiometry above 12 mM. These results confirm the effectiveness of S-vapor annealing in mitigating sulfur vacancies [5], despite minor surface oxidation upon air exposure.

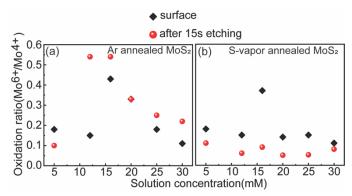

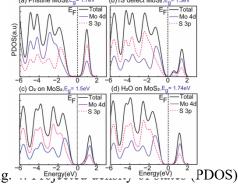

The Mo<sup>6+</sup>/Mo<sup>4+</sup> ratios of Ar and S-vapor annealed MoS<sub>2</sub> films were obtained from the Mo 3d XPS spectra (Fig. 3). Ar-annealed MoS<sub>2</sub> films (Fig. 3a) undergo significant oxidation, with Mo<sup>6+</sup>/Mo<sup>4+</sup> ratios reaching a maximum at ~0.45 around 16 mM and persisting even after etching, indicating interfacial defects and oxygen incorporation. In contrast, S-vapor annealing keeps the ratio below 0.2 (slightly higher at the surface), yielding stoichiometric and chemically stable films above 12 mM as illustrated in Fig. 3b. These results confirm the superior oxidation resistance of S-vapor annealed MoS<sub>2</sub>. Sulfur vacancies in MoS<sub>2</sub> strongly affect its electronic properties and also promote environmental degradation through oxidation. To investigate the impact of these vacancies and the subsequent adsorption of O<sub>2</sub> and H<sub>2</sub>O molecules, density functional theory (DFT) calculations were performed as shown in Fig. 4. PDOS analysis shows that pristine MoS<sub>2</sub> with a band gap (E<sub>g</sub>) of 1.7 eV, has a S-3p dominated valence band and a Mo-4d dominated conduction band with no mid-gap states. Introducing a sulfur vacancy reduces the band gap to 1.3 eV and creates Mo 4d defect states near the Fermi level. O<sub>2</sub> adsorption slightly recovers the gap (1.5 eV) but leaves residual states, indicating poor passivation. In contrast, H<sub>2</sub>O adsorption restores the gap to 1.74 eV, effectively suppressing defect states and providing better passivation.

#### 4. Conclusions

© IWDTF2025 - S5-05 -

\$5-05 IWDTF2025

In conclusion, S-vapor annealing is essential for repairing sulfur vacancies, suppressing oxidation, and achieving near-stoichiometric, crystalline MoS<sub>2</sub> films. This post-synthesis treatment offers a reliable route to structurally and chemically stable MoS<sub>2</sub> for future electronic applications.

#### Acknowledgements

This was supported by MEXT Initiative to Establish Next-generation Novel Integrated Circuits Centers (X-NICS) with grant numbers of JPJ011438.

#### References

- [1] Alam M. I. et al., Sci Rep **2024**, 14 (1), 26779.

- [2] Yun J.-M. et al., J Mater Chem C Mater 2013, 1 (24), 3777.

- [3] Yang, J.; Gu, Y. et al., Nanoscale 2015, 7 (20), 9311-9319.

- [4] Liang, Q. et al., ACS Nano 2021, 15 (2), 2165–2181.

- [5] Zhang, X. et al., Chem Soc Rev 2015, 44 (9), 2757–2785.

Fig. 1: (a) Schematic of the two-zone furnace setup used for sulfur annealing of MoS<sub>2</sub> films and (b) Temperature vs time profile of annealing process.

Fig. 2: Sulfur-to-molybdenum (S/Mo) atomic ratio of MoS<sub>2</sub> films as a function of precursor concentration, extracted from XPS of Mo 3d: (a) Ar-annealed and (b) S vapor-annealed films at 700 °C.

Fig. 3: Mo<sup>6+</sup>/Mo<sup>4+</sup> ratio as a function of solution concentration, extracted from Mo 3d XPS spectra of MoS<sub>2</sub> films grown on Si<sub>3</sub>N<sub>4</sub> surfaces using (a) Ar annealing and (b) S vapor annealing at 700 °C.

(a) Pristine MoS<sub>2</sub> (b) Sulfur defect (1S) defect MoS<sub>2</sub> (c) O<sub>2</sub> adsorbed MoS<sub>2</sub> and H<sub>2</sub>O adsorbed MoS<sub>2</sub> respectively.

© IWDTF2025 - S5-05 -

Session IWDTF2025

Focus Session | Electrically / Physicaly Characterization

**苗** Fri. Nov 7, 2025 10:55 AM - 11:55 AM JST | Fri. Nov 7, 2025 1:55 AM - 2:55 AM UTC **1** 5F-Meeting Room

## [FB] Focus Session B ~ Device Properties under Cryogenic Temperature

Chair: Akio Ohta (Fukuoka University), Takezo Mawaki (Tohoku University)

10:55 AM - 11:25 AM JST | 1:55 AM - 2:25 AM UTC [FB-01]

(invite)Demonstration of Recovery Annealing on 7-Bits per Cell 3D Flash Memory at Cryogenic Operation for Bit Cost Scalability and Sustainability

\*Yuta Aiba<sup>1</sup> (1. Frontier Technology Research & Development Institute., Kioxia Corporation (Japan))

11:25 AM - 11:55 AM JST | 2:25 AM - 2:55 AM UTC [FB-02]

Toward Stable Operation of Si Quantum Computers: Origin of Long-period Charge Fluctuations in Si Fin-type Quantum Dots

\*Hiroshi Oka<sup>1</sup>, Hidehiro Asai<sup>1</sup>, Kimihiko Kato<sup>1</sup>, Takumi Inaba<sup>1</sup>, Shota Iizuka<sup>1</sup>, Yusuke Chiashi<sup>1</sup>, Hitoshi Yui<sup>1</sup>, Shoko Nagano<sup>1</sup>, Shigenori Murakami<sup>1</sup>, Yoshihisa Iba<sup>1</sup>, Minoru Ogura<sup>1</sup>, Takashi Nakayama<sup>1</sup>, Hanpei Koike<sup>1</sup>, Hiroshi Fuketa<sup>1</sup>, Satoshi Moriyama<sup>2</sup>, Takahiro Mori<sup>1</sup> (1. AIST (Japan), 2. Tokyo Denki Univ. (Japan))

FB-01 IWDTF2025

## (invite)Demonstration of Recovery Annealing on 7-Bits per Cell 3D Flash Memory at Cryogenic Operation for Bit Cost Scalability and Sustainability

Yuta Aiba<sup>1</sup>, Hitomi Tanaka<sup>1</sup>, Fumie Kikushima<sup>2</sup>, Toshio Fujisawa<sup>1</sup>, Hiroki Tanaka<sup>1</sup>, and Tomoya Sanuki<sup>1</sup> Frontier Technology Research & Development Institute., Kioxia Corporation, 2-5-1 Kasama, Sakae-ku, Yokohama, Kanagawa-pref, 247-8585 Japan

<sup>2</sup> Memory Div., Kioxia Corporation, 800, Yamanoisshiki-Cho, Yokkaichi, Mie-Pref, 512-8550, Japan E-mail: yuta1.aiba@kioxia.com

#### 1. Introduction

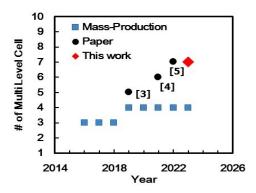

NAND Flash memory is one of the lowest cost and highest bit density nonvolatile memory [1, 2]. Although the bit cost scaling has been achieved so far by highly stacked word lines (WL), the increase of fabrication cost will make it difficult in near future. Therefore, there is a need for an alternative scaling technology without increasing the process steps and fabrication cost, such as the multi-level cell [3] (Fig. 1). We previously reported that cryogenic operation of 3D flash memory at 77 K could achieve 6-bits [4], and 7-bits per cell by utilizing epi-Si channel [5]. However, it was based on a relatively fresh device before P/E cycle degradation, and therefore reliability characteristics remains to be improved for practical use. In this report[6], we describe that the P/E cycle degradations of cell characteristics can be recovered by annealing and present a novel countermeasure to achieve reliable 7-bits per cell operation.

#### 2. Experimental Result

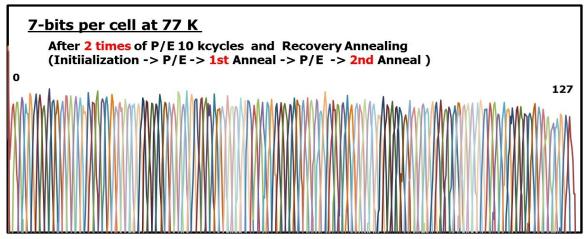

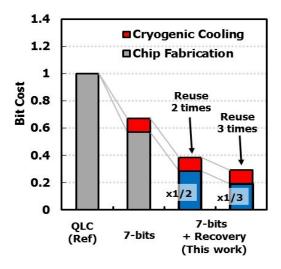

We conducted an experiment to evaluate the storage performance degradation caused by write/erase cycles at cryogenic temperature and apply recovery annealing. As a result, we found that a relatively low temperature and short annealing time of 3 hours at 200°C with appropriate data written during annealing can fully recover memory cell characteristics. Fig.2 shows a successful demonstration of 7-bits per cell at 77 K after 2 times of both P/E 10 k cycles and recovery annealing. Even after a total 20k write/erase cycles, a tight distribution of 128 Vths (equivalent to 7 bits) was achieved, with performance equivalent to the initial state. Fig.2 shows the degradation of program noise due to P/E cycles and recovery after annealing. The effect of recovery annealing is repeatable, indicating that the memory chip can be reusable. Fig.3 shows the bit cost, which includes bit fabrication cost and cryogenic cooling cost. Reuse enabled by the recovery annealing can further reduce bit cost since there is no need for fabrication. It becomes one-half or one-third by reusing a device 2 times or 3 times, respectively.

#### 3. Conclusions

In this paper, 7-bits per cell at cryogenic operation of 77 K combined with the recovery annealing is reported. These technologies can make the future 3D flash memory further bit-cost scalable and sustainable.

#### References

- [1] F. Masuoka et al., IEDM 1987, pp. 552-555(1987).

- [2] H. Aochi, IMW 2009, pp. 1-2(2009).

- [3] K. Ishimaru, IEDM 2019, pp.12(2019).

- [4] Y. Aiba et al., EDTM 2021, pp. 1-3(2021).

- [5] H. Tanaka et al., IMW 2022, pp. 1-4(2022).

- [6] Y. Aiba et al., VLSI, pp.1-2 (2023)

© IWDTF2025 - FB-01 -

FB-01 IWDTF2025

Fig. 1 Multi-level cell has been achieved continuously from 5-bits per cell to 7-bits per cell. [6] Y. Aiba et al., VLSI, pp.1-2 (2023)

Copyright (2023) The Japan Society of Applied Physics

Fig. 2 Demonstration of 7-bits per cell at 77 K with epi-Si channel after 2 times of both P/E 10k cycles and recovery annealing.

[6] Y. Aiba et al., VLSI, pp.1-2 (2023)

Copyright (2023) The Japan Society of Applied Physics

Fig.3 Future bit cost scaling is achieved by both 7-bits per cell at cryogenic operation and reuse by applying recovery annealing.

[6] Y. Aiba et al., VLSI, pp.1-2 (2023)

Copyright (2023) The Japan Society of Applied Physics

© IWDTF2025 - FB-01 - FB-02 IWDTF2025

## Toward Stable Operation of Si Quantum Computers: Origin of Long-period Charge Fluctuations in Si Fin-type Quantum Dots

Hiroshi Oka<sup>1</sup>, Hidehiro Asai<sup>1</sup>, Kimihiko Kato<sup>1</sup>, Takumi Inaba<sup>1</sup>, Shota Iizuka<sup>1</sup>, Yusuke Chiashi<sup>1</sup>, Hitoshi Yui<sup>1</sup>, Shoko Nagano<sup>1</sup>, Shigenori Murakami<sup>1</sup>, Yoshihisa Iba<sup>1</sup>, Minoru Ogura<sup>1</sup>, Takashi Nakayama<sup>1</sup>, Hanpei Koike<sup>1</sup>, Hiroshi Fuketa<sup>1</sup>, Satoshi Moriyama<sup>2</sup>, and Takahiro Mori<sup>1</sup>

<sup>1</sup> National Institute of Advanced Industrial Science and Technology (AIST), Tsukuba, Japan <sup>2</sup>Department of Electrical and Electronic Engineering, Tokyo Denki University (TDU), Tokyo, Japan email: oka.hiroshi@aist.go.jp

#### 1. Introduction

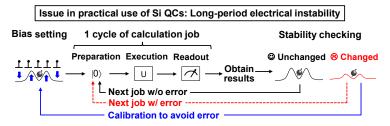

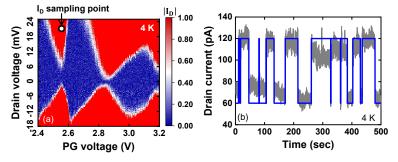

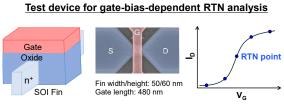

Si quantum computers (QCs) have attracted considerable attention due to their scalability potential to achieve the large-scale integration of Si spin qubits using CMOS manufacturing technology. Recently, there has been several progresses in the performance of Si spin qubits, such as two-qubit gates operation with fidelity over 99%[1] and prolonged coherence time T<sub>2</sub>\* of 120 µsec [2]. From the standpoint of practical use, the electrical stability of qubits is a critical issue that needs to be addressed, as they necessitate frequent monitoring and calibrations of the qubit parameters (Fig. 1). Indeed, some superconducting QCs already in commercial use are calibrated every few hours, preventing the stable operation and limiting the available time slot. However, the electrical stability of Si spin qubits, i.e., long-period charge fluctuation, has not been thoroughly discussed until now. In this study, we conducted an in-depth analysis of the electrical stability of the fin-type Si quantum dots (QDs), which is a promising host for spin qubits. We performed gate-bias-dependent random telegraph noise (RTN) measurements to clarify the physical origin of the long-period charge fluctuation of fin-type QDs for the first time.

#### 2. Experimental Procedure

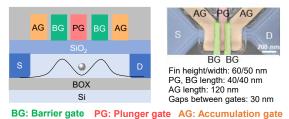

Fin-type QDs were fabricated on p-type SOI wafers ( $T_{SOI}$ =60 nm,  $T_{BOX}$ =145 nm) with a 12-nm-thick SiO<sub>2</sub>/poly-Si gate (Fig. 2). A plunger gate (PG), barrier gates (BGs), and accumulation gates (AGs) were formed on the fin to confine electrons under the PG. The measurements were performed at 4 K using a cryogenic prober. We confirmed successful single-electron transport at 4 K with fabricated fin-type QDs from the charge stability diagram shown in Fig. 3(a). Figure 3(b) shows the drain current ( $I_D$ ) transient at a fixed gate bias. A distinct two-level transition was observed with an ultralow frequency of < 0.05 Hz, which would become a critical issue for the stable operation of Si QCs. As the QDs have multiple gates and different bias conditions are used for single-electron transport, it is very difficult to identify the origin of charge fluctuation by the QD measurement alone. Thus, we fabricated the single-gate test device having the same fin and gate structure as QDs, enabling the gate-bias-dependent RTN analysis to reveal the trap states inducing the long-period charge fluctuations (Fig. 4).

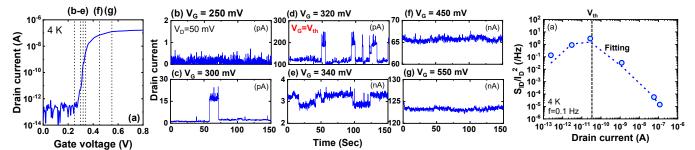

#### 3. Results and Discussion

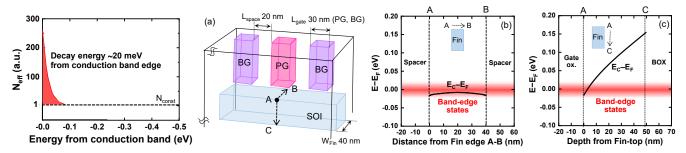

Figure 5(a) shows the I<sub>D</sub>-V<sub>G</sub> characteristic of a single-gate test device at 4 K. Captured I<sub>D</sub> transients at different gate bias conditions from off-state to on-state bias are shown in Figs. 5(b) to 5(g). A distinct multilevel transition was observed at bias conditions of 300, 320, and 340 mV. These are close to V<sub>th</sub> of 320 mV, and we confirmed the long-period charge fluctuation occurred only at certain bias conditions. We extracted the power spectral density (S<sub>ID</sub>) from the Fourier transform of the I<sub>D</sub> transient (Fig. 6). The S<sub>ID</sub> showed drain current dependence and increased by more than one order of magnitude toward Vth. As the SID is proportional to the effective trap density (Neff) in the carrier number fluctuation (CNF) model [3], the obtained results indicate that N<sub>eff</sub> is increased near V<sub>th</sub>. From the fitting of the S<sub>ID</sub> -I<sub>D</sub> plot based on the CNF model, we extracted the energetic distribution of trap states inducing excess noise near V<sub>th</sub>. We found the exponentially distributed trap states with shallow decay energy of 20 meV at the conduction band edge are responsible for the charge fluctuation observed near V<sub>th</sub> (Fig. 7). To reveal where long-period charge fluctuation occurs in fin-type QDs, we performed a simulation of single-electron transport by using an in-house TCAD simulator [4]. Figure 8 shows the simulated Fermi level (E<sub>F</sub>) position along the fin-width (A-B) and fin-depth (A-C) directions. We found the E<sub>F</sub> aligns to the band edge states in the whole area of the top-surface of the fin, while that of the side-surface is mostly far from the band edge states. This means the long-period charge fluctuations mainly occur at the top-surface of the fin rather than its side-surface. Since the band edge states are strongly related to the quality of the MOS interface [5], these results imply that the MOS interface engineering at the top-surface of the fin is critical to improve the electrical stability of the fin-type QDs.

© IWDTF2025 - FB-02 -

FB-02 IWDTF2025

#### 4. Conclusions

We conducted the first experimental verification on the long-period charge fluctuation of fin-type QDs, whose origin is band edge states located at the top-surface of the fin, suggesting that even more care of the MOS interface at the fin-top is necessary to provide better stability. We believe that the obtained knowledge paves the way to realize stable quantum computation with Si spin qubits.

**Acknowledgements** This work is based on the results obtained from the MEXT Q-LEAP Grant No. JPMXS0118069228, Japan.

**References** [1] A. R. Mills *et al.*, Sci. Adv. **8**, eabn5130 (2022). [2] M. Veldhorst *et al*, Nat. Nanotechnol. **9**, 981 (2014). [3] G. Ghibaudo *et al.*, Phys. Stat. Solidi (a) **124**, 571 (1991). [4] H. Asai *et al.*, Jpn. J. Appl. Phys. **62**, SC1088 (2023). [5] H. Oka *et al.*, Tech. Dig. IEDM, 22-6 (2023).

Fig. 1 The aim of this study is to clarify the origin of long-period charge fluctuation of Si QDs that necessitates frequent monitoring and calibration during its running time.

Fig. 2 Fabricated fin-type QDs on SOI wafer. The gate bias condition was chosen to confine an electron using a potential barrier formed by PG, BG, and AG.

Fig. 3 (a) Charge stability diagram of fin-type QDs. (b) I<sub>D</sub> transient of fin-type QDs with gate bias condition indicated in (a).

Fig. 4 Single-gate test device, which is fabricated on the same wafer with the same process as the fin-type QDs. Gate-bias-dependent RTN analysis was conducted to clarify the origin of charge fluctuation.

Fig. 5 (a)  $I_D$ - $V_G$  curve and transient of  $I_D$  of single-gate test device at 4 K with gate bias of (b) 250 mV, (c) 300 mV, (d) 320 mV, (e) 340 mV, (f) 450 mV, and (g) 550 mV. Trapping/de-trapping events observed only near the  $V_{th}$  operation.

Fig. 6  $I_D$  dependence of  $S_{ID}/I_D^2$ . Excess noise appeared near  $V_{th}$ . The fitting curve is also shown.

Fig. 7 Extracted energetic distribution of trap states from fitting of  $S_{ID}$  shown in Fig. 6.

energetic Fig. 8 (a) Structure of simulated fin-type QDs. Simulated energy level of  $E_C$  relative to ates from  $E_F$  ( $E_C$ – $E_F$ ) along with (b) fin width A-B and (c) fin depth A-C. Position for conduction band edge operation ( $E_F$ – $E_C$  <20 meV) is marked by red areas.

© IWDTF2025 - FB-02 -

Session IWDTF2025

Power Device & Processes | Electron device, process, and characterization

**ਛ** Fri. Nov 7, 2025 1:30 PM - 3:10 PM JST | Fri. Nov 7, 2025 4:30 AM - 6:10 AM UTC **逾** 5F-Meeting Room

## [S6] Power Device & Processes (1)

Chair: Motoyuki Sato (Tokyo Electron), Toshinori Numata (Toyota Technological Institute)

1:30 PM - 2:00 PM JST | 4:30 AM - 5:00 AM UTC [S6-01]

Carbon P<sub>b</sub> centers in 4H-SiC/SiO<sub>2</sub> interface

\*Takahide Umeda Umeda<sup>1</sup>, Mitsuru Sometani<sup>2</sup>, Bunta Shimabukuro<sup>1</sup>, Yusuke Nishiya<sup>3</sup>, Yu-ichiro Matsushita<sup>3</sup> (1. Univ. of Tsukuba (Japan), 2. AIST (Japan), 3. Quemix Inc./Tokyo Univ. (Japan))

$2:\!00$  PM -  $2:\!20$  PM JST |  $5:\!00$  AM -  $5:\!20$  AM UTC

[S6-02]

Study on Possible Origin of Improved 4H-SiC (0001) MOS Interface Characteristics with Direct NO Oxynitridation Based on Consideration of Oxinitride Growth Kinetics

\*Yutaro Uchida<sup>1</sup>, Atsushi Tamura<sup>1</sup>, Koji Kita<sup>1</sup> (1. The Univ. of Tokyo (Japan))

2:20 PM - 2:40 PM JST | 5:20 AM - 5:40 AM UTC

[S6-03]

Impact of Substrate-Surface Oxidation Treatment and Post-Deposition Annealing on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (001) MOS Interfaces with ALD-Deposited Al<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub>

\*Atsushi Tamura<sup>1</sup>, Hayama Imaida<sup>1</sup>, Hiroyasu Maekawa<sup>2</sup>, Koji Kita<sup>1,2</sup> (1. Dept. of Advanced Materials Science, The Univ. of Tokyo (Japan), 2. Dept. of Materials Engineering, The Univ. of Tokyo (Japan))

$2{:}40~\text{PM}$  -  $3{:}10~\text{PM}$  JST  $|~5{:}40~\text{AM}$  -  $6{:}10~\text{AM}$  UTC

[S6-04]

Exploration of new materials for meta-materials and power semiconductor applications

\*Kentaro Kaneko<sup>1</sup> (1. Ritsumeikan Univ. (Japan))

\$6-01 IWDTF2025

#### Carbon P<sub>b</sub> centers in 4H-SiC/SiO<sub>2</sub> interface

T. Umeda<sup>1</sup>, M. Sometani<sup>2</sup>, B. Shimabukuro<sup>1</sup>, Y. Nishiya<sup>3</sup>, and Yu. Matsushita<sup>3</sup>

<sup>1</sup>Univ. of Tsukuba, <sup>2</sup>AIST, <sup>3</sup>Quemix Inc./Tokyo Univ.

<sup>1</sup>1-1-1 Ten-nodai, Tsukuba, 305-8567, Japan.

<sup>2</sup>16-1 Onogawa, Tsukuba, 305-8569, Japan.

<sup>3</sup>Taiyo Life Nihombashi Building, 2-11-2, Nihombashi Chuo-ku, Tokyo 103-0027, Japan. Email: umeda.takahide.fm@u.tsukuba.ac.jp / Phone: +81-29-859-5330

#### 1. Introduction

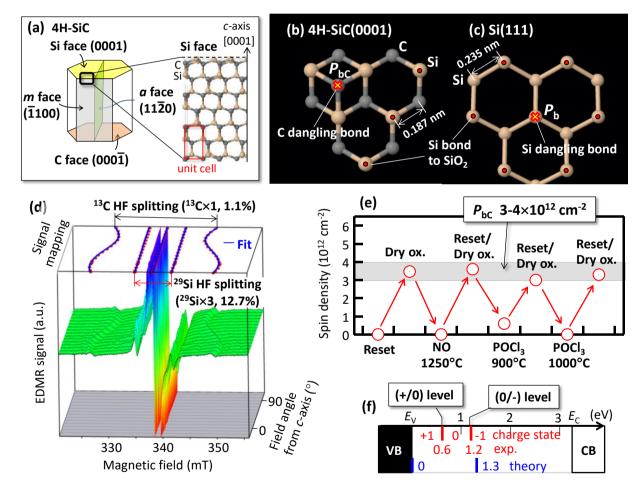

Out invited talk focuses on new and published results for carbon  $P_b$  centers ("the  $P_{bC}$  centers") in SiC MOS (metal-oxide-semiconductor) structures. The  $P_{bC}$  center is a carbon version of the famous  $P_b$  centers (Si dangling bonds) at Si/SiO<sub>2</sub> interfaces [1], and we can point out not only many similarities between  $P_{bC}$  and  $P_b$  but also their dissimilarities, in other words, differences between SiC and Si.

Before presenting the  $P_{bC}$  centers, we would like to introduce 4H-SiC material itself. 4H-SiC is a wide-gap semiconductor ( $E_g = 3.26 \, \text{eV}$ ), showing many unique and interesting properties; such as its useful MOS structure with thermal oxidation, a wide-range capability of ion-implantation doping from n+ to p+, large-sized single-crystal wafers, etc. These features make 4H-SiC being a leading wide-gap semiconductor for the next-generation power electronics, enabling its industrial applications to inter-city transportations (e.g., Yamanote-Line), high-speed trains (e.g., Shinkan-sen N700S), and electric vehicles (e.g., Tesla EVs), and so on. The power 4H-SiC MOSFETs with 600V or 1200V voltage range are representative devices. Such power MOSFETs, however, still suffer from many unresolved issues in their performance and reliability. Most of the issues are related to MOS interface defects or interface states (Dit). Therefore, many studies continuously challenge to clarify origins of Dit, how to control (remove) them, and their roles/influences on SiC MOSFETs. The  $P_{bC}$  center shown here is a unique example in wide-gap semiconductors, whose properties (origin [2], density [3], energy levels [4], reactivity [3,5,6], etc.) are clearly revealed as comparable as those of the  $P_b$  center in Si-MOS systems.

#### 2. What is the $P_{\rm bC}$ center?

The  $P_{bC}$  center was found in 4H-SiC(0001) face ["Si face", Fig. 1(a)] after thermal oxidation. We can observe it by using electron-spin-resonance (ESR) or electrically-detected ESR (EDMR) spectroscopy. Its origin is a carbon dangling bond normal to the Si face [2] [Fig. 1(b)], which looks like very similar to the famous  $P_b$  center at Si(111)/SiO<sub>2</sub> interfaces [1] [Fig. 1(c)]. They are assigned to be Si<sub>3</sub> $\equiv$ C• and Si<sub>3</sub> $\equiv$ Si•, respectively ("•" indicates an unpaired spin). Their typical densities are comparable:  $3-4\times10^{12}$  cm<sup>-2</sup> [3] and  $1-4\times10^{12}$  cm<sup>-2</sup> [1], despite 4H-SiC(0001) lattice is much denser than that of Si(111). This comparability suggests more efficient structural relaxation around  $P_{bC}$  as compared to the case of  $P_b$ . We pointed out that the  $P_{bC}$  center is formed at a carbon adatom (C<sub>adatom</sub>) on the Si face. This structure has a great advantage of decreasing Si bonds to the SiO<sub>2</sub> layer [Fig. 1(b)], leaving a single dangling bond on C<sub>adatom</sub>. Furthermore, it has another merit to utilize residual carbon atoms emitted during the oxidation process. Figure 1(d) shows an enlarged view (×10) of an EDMR signal of the  $P_{bC}$  center. We successfully detected hyperfine (HF) splittings due to <sup>13</sup>C nuclear spin at C<sub>adatom</sub> and <sup>29</sup>Si nuclear spins at three Si back-bonds. The observed HF splittings well agreed with the theoretical ones for the C<sub>adatom</sub> structure [2]. Furthermore, we also revealed chemical reactivities of  $P_{bC}$  for many processes, like shown in Fig. 1(e) [3,5,6].

Energy levels of  $P_{bC}$  have been experimentally determined [4], likewise the case of  $P_{bC}$ . The  $P_{bC}$  center shows three possible charge states, +1 (no electron/spin=0), 0 (one electron/spin=1/2), and -1 (two paired electrons/spin=0), as shown in Fig, 1(f). Thus, the (+/0) and (0/-) levels are determined to be  $E_{V}$ +0.6 eV and  $E_{V}$ +1.2 eV, respectively. This is the world-first data on a direct relationship between Dit and interface defects in wide-gap semiconductors. Using this benchmark result, we also examine highly-accurate first-principles calculations (based on HSE06 functionals) on  $P_{bC}$  [4]. The calculated results are also shown in Fig. 1(f), where we find a significant discrepancy, indicating a limitation that the state-of-the-art calculations still include problems for predicting interface states.

#### 3. Two types of the $P_{\rm bC}$ centers

On 4H-SiC(0001) face, there is another  $P_{bC}$  center, which we name " $P_{bC}$ -type2 center." As shown in Fig, 1(f), the primary type noted above (we call it " $P_{bC}$ -type1" hereafter) has  $E_{V}$ -side interface states. On the other hand, the  $P_{bC}$ -type2 center exhibits  $E_{C}$ -side interface states [7]. The reasons why two types of  $P_{bC}$  exist in 4H-

© IWDTF2025 - S6-01 -

\$6-01 IWDTF2025

SiC, why their energy levels are so different, and what are their influences on 4H-SiC MOSFETs, are discussed in the presentation.

#### Acknowledgements

This work was supported by CSTI SIP program, "Next-generation power electronics", and also partly by MEXT Grant-in-Aids 18H03770, 18H03873, 17H02781, 20H00340, 21H04553 and JP-MXP1020200205. The authors also acknowledge many other collaborators listed as co-authors in our published papers.

#### References

- [1] P. M. Lenahan et al., J. Vac. Sci. Technol. B 16, 2134 (1998).

- [2] T. Umeda et al., Appl. Phys. Lett. 116, 071604 (2020)

- [3] T. Umeda et al., Appl. Phys. Lett. 113, 061605 (2018).

- [4] M. Sometani et al., APL Mater. 11, 111119 (2023).

- [5] T. Umeda et al., J. Appl. Phys. 127, 145301 (2020).

- [6] E. Higa et al., Appl. Phys. Lett. 116, 171602 (2020).

- [7] B. Shimabukuro et al., ICSCRM2024 (Sep. 29 to Oct. 2, 2024, Raleigh, USA).

Fig. 1 The carbon  $P_b$  center ( $P_{bC}$  center) at 4H-SiC(0001)/SiO<sub>2</sub> interface. (a) 4H-SiC single-crystal system. (b)  $P_{bC}$  center at 4H-SiC(0001) face. (c)  $P_b$  center at Si(111) face. (d) EDMR spectra of  $P_{bC}$  observed using dry-oxidized 4H-SiC(0001) MOSFET (maximum field-effect mobility = 8 cm<sup>2</sup>/V/s) [2]. (e) Chemical reactivity of  $P_{bC}$  [3]. (f) Energy levels of  $P_{bC}$  [4].

© IWDTF2025 - \$6-01 -

\$6-02 IWDTF2025

## Study on Possible Origin of Improved 4H-SiC (0001) MOS Interface Characteristics with Direct NO Oxynitridation Based on Consideration of Oxinitride Growth Kinetics

Yutaro Uchida\*, Atsushi Tamura and Koji Kita

Department of Advanced Materials Science, The University of Tokyo

5-1-5 Kashiwanoha, Kashiwa-shi, Chiba 277-8561, Japan

Email: uchida-yutaro0144@g.ecc.u-tokyo.ac.jp / Phone: +81-4-7136-5456

#### 1. Introduction

In SiC power MOSFETs, one of the commonly employed methods to form MOS interfaces is the thermal oxidation, followed by NO annealing which enables an efficient passivation of MOS interface defects by replacing a part of the topmost C atoms on SiC by N. The N density introduced by this process is known to be saturated to a certain value [1]. On the other hand, the direct NO oxynitridation of 4H-SiC substrates to form a SiO(N) film has a potential to be an alternative process [2]. Since the kinetics of the N atom introduction on SiC surface should differ between the direct nitridation on the surface and the nitridation through a thick-SiO<sub>2</sub> layer, the electrical properties of the formed interfaces will be also different. In this study, we investigated both the kinetics of the direct NO oxynitridation and the interface characteristics of MOS capacitors employing the oxynitride as the interface layer.

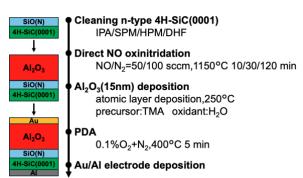

#### 2. Experimental Procedure

4° off-axis n-type 4H-SiC (0001) Si-face wafers with epitaxial layers ( $N_D \sim 1 \times 10^{16}$  cm<sup>-3</sup>) were used as substrates. After cleaning in diluted HF, the wafers were directly oxynitrided at 1150°C for various durations in NO:N<sub>2</sub>=1:2 ambient to form SiO(N) films. The grown film thickness and N density on SiC substrate were evaluated by X-ray reflectivity and a ratio of N 1s / Si 2p XPS intensities, respectively. Next, on the SiO(N) film formed by direct NO oxynitridation as described above, a 15-nm-thick-Al<sub>2</sub>O<sub>3</sub> layer was deposited at 250°C with atomic layer deposition using TMA and H<sub>2</sub>O as oxidant as shown in **Fig. 1**. Subsequently, the samples were annealed in 0.1%-O<sub>2</sub>+N<sub>2</sub> ambient at 400 – 600°C, followed by a deposition of Au electrodes to form MOS capacitors. For comparison, a sample was also fabricated by thermal oxidation in O<sub>2</sub> followed by NO annealing at 1150°C for 120 min.

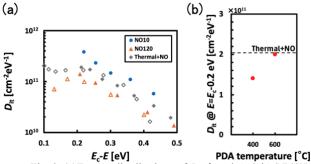

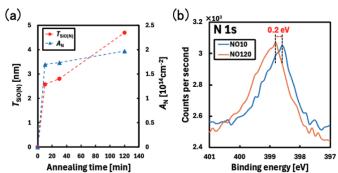

#### 3. Results and Discussion

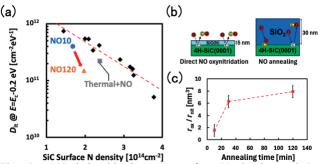

The time dependent change of SiO(N) film thickness grown on the substrate by the direct NO oxynitridation is shown in Fig. 2(a). In the initial 10 min, the growth rate of the SiO(N) film by direct NO oxynitridation at 1150°C was high, to achieve a film thickness of ~2.5 nm rapidly. After that it slowed down significantly and the film thickness reached only about 5 nm even after as long as 120 min oxynitridation. Next, the SiO(N) films were removed by HF etching, and the N density on SiC substrate surface was evaluated by XPS. The density shown on the righthand side axis in Fig. 2(a) was estimated based on the previously determined relationship between N 1s / Si 2p intensity ratio and the surface N areal density determined by high-resolution RBS in our group. The nitrogen incorporation proceeds rapidly in the initial stage, with the surface N areal density reaching  $\sim 1.7 \times 10^{14}$  cm<sup>-2</sup> within 10 minutes, after which it quickly saturates. It is different from a gradual increase of N density for the case of conventional NO annealing of a thick-SiO<sub>2</sub>/SiC stacks [1] (data not shown). It should be noted that the ratio of the oxidation rate to the nitridation rate is small in the initial stage with rapid nitrogen incorporation but significantly increases in the latter stage as will be discussed later. The N 1s core level XPS after removal of surface oxide is shown in Fig. 2(b) for the oxynitridation durations of 10 min (NO10) and 120 min (NO120). Compared with NO10, the peak of NO120 shifts to a lower binding energy by ~0.2 eV when the binding energy was calibrated by the Si 2p substrate peak. It is considered that N-Si bonds are predominant in NO10, whereas the fractrion of N-O bonds increases in NO120.

The energy distributions of  $D_{it}$  determined by the conductance method for the MOS capacitors after PDA at 400°C are shown in Fig. 3(a). It should be noted that NO120 showed a lower  $D_{it}$  than the reference sample of conventional NO annealing after thermal oxidation (Thermal+NO), while the NO10 exhibited a higher  $D_{it}$  than that. This indicates that the long-time oxynitridation is required to reduce the interface trap density, although the relatively high N surface density was achieved even with a short-time direct NO oxynitridation. Fig. 3(b) shows the comparison of  $D_{it}$  at  $E = E_c - 0.2$  eV for Al<sub>2</sub>O<sub>3</sub>/SiO(N)/4H-SiC(0001) MOS capacitors annealed in 0.1%-O<sub>2</sub>+N<sub>2</sub> ambient at 400°C or 600°C. This result revealed that PDA at 600°C leads to a slight increase of  $D_{it}$  from that obtained at 400°C, while  $D_{it}$  value remains comparable to that of Thermal+NO, which indicates that the passivation process of SiO<sub>2</sub>/SiC interface defects by NO does not have to be conducted as the final step of the process.

Figure 4(a) shows the relationship between the N surface density on SiC and  $D_{it}$  at  $E = E_c - 0.2$  eV. The dashed line in the figure represents the trend of the results obtained by our previous work for the cases of annealing of thermal oxide films in N<sub>2</sub>+O<sub>2</sub> ambient under various conditions [3]. It revealed that  $D_{it}$  of NO120 was approximately one third of the value expected from the trend of the previous work for the identical surface N density, indicating that the improved interface characteristics of the NO120 should not be attributed solely to the increase in surface N density.

© IWDTF2025 - \$6-02 -

\$6-02 IWDTF2025

The origins of the improved interface quality with a lower  $D_{it}$  of NO120 would be explainable by two possible factors. First, the growth rate of the SiO(N) film significantly slows down at ~2.5 nm as discussed above, and the oxidation of SiC proceeds slowly in the latter stage of the oxynitridation. Since such a SiO(N) layer would be thin enough for the carbon byproduct desorption through the layer, more efficient desorption of excess C atoms at the interface would occur, enabling a further reduction of the interface defect density (**Fig. 4(b)**). Second, as shown in **Fig. 4(c)**, the ratio of the oxidation rate to the nitridation rate significantly increases in the latter stage. The formation of interface with not only N-Si but also a certain fraction of N-O bonds may play a role in stabilizing the N-passivated interface structure and enhancing the interface properties.

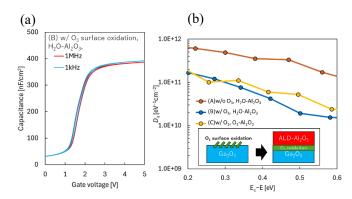

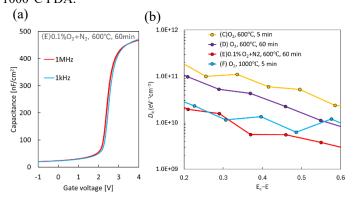

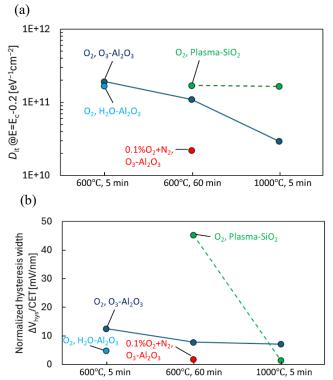

#### 4. Conclusions