## 極低温下でのホットキャリア注入に起因した巨大なしきい値電圧変動の理解

Understanding Large V<sub>th</sub> Shift by Hot Carrier Injection at Cryogenic Temperatures 產総研¹, 慶大物情² <sup>O</sup>(D) 下方駿佑¹², 岡博史¹, 加藤公彦¹, 稲葉エ¹, 飯塚将太¹, 浅井栄大¹, 森貴洋¹ AIST¹, APPI, Keio², °S. Shitakata¹², H. Oka¹, K. Kato¹, T. Inaba¹, S. Iizuka¹, H. Asai¹, and T. Mori¹ E-mail: s-shitakata@aist.go.jp

大規模量子コンピュータの実現には、室温からの熱流入を削減しながら量子ビットの状態の制御・読出を行うクライオ CMOS 集積回路技術が不可欠である。MOSFET の極低温動作の理解が求められるが、近年の研究では、しきい値電圧( $V_{th}$ )の温度依存他の様々な特性にバンド端準位が強く影響することが明らかになってきた[1,2]。一方で、信頼性に関連する議論は始まったばかりであり、これまでにはホットキャリアによる特性劣化(Hot Carrier Degradation; HCD)が低温で増大することが報告されているが[3]、そのメカニズムは明らかではない。そこで本研究では、ホットキャリア注入後の $V_{th}$ 変動の温度依存性を評価し、また極低温下では有効性が未検証である重水素( $D_2$ )アニールによる劣化抑制効果[4]を試験することで、メカニズムの理解を試みた。実験には、(100)面がルクシリコンウエハ(10) 型、100 型、

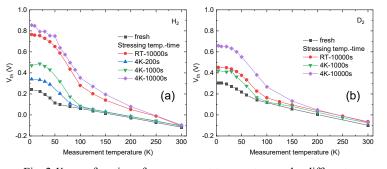

実験には、(100)面バルクシリコンウエハ(p 型、 $1\sim5\Omega$ cm)に poly-Si/熱酸化 SiO<sub>2</sub> ゲートスタックのセルフアラインプロセスで作製した n-MOSFET を用いた。酸化膜厚は 8nm である。電極形成後に水素 $(H_2)$ または  $D_2$  フォーミングガスアニール(FGA)をそれぞれ 400°C で 30 分間行った。作製した試料(f 一ト長  $1\mu$ m)に対して、室温または 4K でのホットキャリアストレス印加 $(V_D, stress=6.5V, V_G, stress=2.3V)$ を行った。その後各温度でストレス印加した試料について、温度 $(T_m)$ を変化させ電気特性の評価を行った(図 1)。

まず  $H_2$  FGA 試料について、4K でのストレス印加後は、既報告[3]にあるような大きな  $V_{th}$  変動が観測された。ストレス印加時間( $I_{tress}$ )であっても、室温に戻すと  $V_{th}$  の変化量は微少になっていることがわかる(紫線)。 一方、室温でのストレス印加時間( $I_{tress}$ )であっても、室温に戻すと  $V_{th}$  の変化量は微少になっていることがわかる(紫線)。 一方、室温でのストレス印加試別についても同様に  $V_{th}$  温度依存性をみると、ほぼ同一の傾向を示している(赤線)。このことから、ストレス印加温度に関わらず、同一描像の界面劣化が発生していると考えられる。一方で、 $V_{th}$  に与える影響は、ストレス印加温度によって異なることが示唆される。ここで得られた  $V_{th}$  で加温度依存性であり、バンド端準位密度に依存すると考えられている[1,2]。この  $V_{th}$  の上昇量はストレス印加時間に相関する(青線、緑線、紫線)ことから、極低温下で見られる巨大な  $V_{th}$  変動は、バンド端準位の増加に起因すると考えられる。こで注目すべきは、今回のストレス時間は、印加温度によらず、室温では I0mV 以下の微少な  $V_{th}$  変動しか起こさない時間であるということである。それにも関わらず、4K では I00mV 以上の巨大な  $V_{th}$  変動が発生している。室温における HCD は界面ダングリングボンド欠陥の増加に起因すると考えられているが[4]、これとはまるで独立するように 4K での  $V_{th}$  変動が発生している。すなわち、4K での  $V_{th}$  変動の原因と考えられるバンド端準位量の増大は、界面ダングリングボンド欠陥量の増大以上に発生しているものと考えられる。次に、室温においては I00mV 以上の方なわち、I00mV 以上に発生しているものと考えられる。次に、室温においては I00mV 以上の変動は I00mV 以上の方なわち、I00mV I00mV I00mV

以上まとめると、HCD による極低温下での  $V_{th}$  増大現象は、バンド端準位の増加が原因であることがわかった。これは、HCD によるダングリングボンドの発生量とは比例していないと考えられる。一般に HCD を抑制する  $D_2$  アニールは、AK ストレス印加においては効果が薄く、これはフォノン周波数の温度依存に起因すると考えられる。

【謝辞】本研究は NEDO の委託業務(JPNP16007)および文部科学省 Q-LEAP(JPMXS0118069228)の助成を受けて実施した研究の結果得られたものである。本研究におけるデバイス試作は、産業技術総合研究所・未踏デバイス試作共用ライン(COLOMODE)にて実施された

【参考文献】 [1] A. Beckers et al., IEEE-JEDS **8**, 780 (2020). [2] H. Oka et al., IEDM 2023. [3] Y. Zhang et al., IEEE-TDMR **21**, 620 (2021). [4] J. W. Lyding et al., APL **68**, 2526 (1996). [5] C. G. Van de Walle and W. B. Jackson, APL **69**, 2441 (1996).

Fig. 1 Experimental procedure of this study.

Fig. 2 V<sub>th</sub> as a function of measurement temperature under different stress condition (temperature and time) for (a) H<sub>2</sub> FGA and (b) D<sub>2</sub> FGA.