# 0-0-π SQUID の周回電流の向きが半磁束量子論理ゲートに及ぼす影響 Effect of directions of circulating currents in 0-0-π SQUIDs on half-flux-quantum logic gates 名大院工 <sup>○</sup>出口創万, 佐藤太一, 堀裕貴, 西崎海, 李峰, 田中雅光, 藤巻朗 Nagoya Univ, <sup>○</sup>Soma Deguchi, Taichi Sato, Hiroki Hori, Kai Nishizaki, Feng Li, Masamitsu Tanaka, and Akira Fujimaki

E-mail: deguchi@super.nuee.nagoya-u.ac.jp

## 背景

$\pi$  接合を含む SQUID 内部には量子化条件により自発的に周回電流が生じ、見かけの臨界電流値が下がり、小さな駆動力でスイッチさせることができる。このことを利用し、半磁束量子(HFQ)回路は、単一磁束量子(SFQ)回路よりも 1 桁程度低い消費電力性を実現できる[1]。一方、 $\pi$ 接合を含む SQUID が  $\pi$ /2 程度の初期位相差を持つため、HFQ回路の設計では位相調整が格段に難しい。また、SQUID に非対称性があると、隣接している SQUID に流れる周回電流の向きの組合せによっても位相差に違いが生じるため、回路の振る舞いは更に複雑になる。我々はこれまでに、非対称性が信号伝送回路の遅延時間に与える影響を報告している[2]。今回は、より複雑な論理ゲートにおける影響を回路シミュレーションにより調査した。

#### シミュレーション

通常の接合(0 接合)と  $\pi$  接合の臨界電流値を完全に一致させることは困難なため、本研究では大きな臨界電流値を持つ  $\pi$  接合をスイッチさせない位相シフタとして用い、2つの 0 接合をスイッチ素子とする 0-0- $\pi$  SQUID で HFQ 回路を構成する。HFQ 回路は情報担体に $\phi_0$ /2の磁束を用いており、0-0- $\pi$  SQUID がスイッチすると内部の周回電流の向きが切り替わり,位相差が  $\pi$  だけ変化する。 $\pi$  接合が非線形のインダクタンスを持つため、0-0- $\pi$  SQUID は非対称性を持ち[3]、位相変化やスイッチ動作の振る舞いは周回電流の向きに依存する。

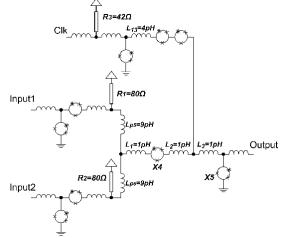

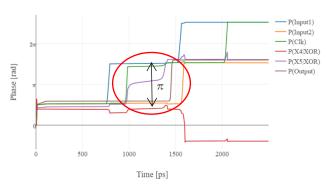

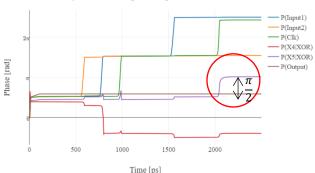

この影響を調べるため、Fig.1に示したXOR論理ゲート のシミュレーションを行った。典型的な 0-0-π SQUID にお ける 0 接合と  $\pi$  接合の臨界電流値はそれぞれ  $60\mu$ A と 2mA で、見かけの臨界電流値は 20µA 前後である。バイアス電 圧の設計値 0.5mV に対し, 0.048mV を印加し、入力(Input1, Input2)に(1,0),(1,1)の順で入力したときの位相変化を Fig. 2 に示す。クロック信号 Clk を入力したとき、X5 の 0-0-π SQUID がスイッチし、位相差πが生じるのが正常な動作で ある。はじめに(1,0)を入力すると、X5 の位相差が  $\pi$  増加し、 出力が得られている。その後の(1,1)を入力した後に Clk を 入力すると、出力が得られず、適切な動作をしている。一 方で Fig. 3 は入力(Input1, Input2)に(1,1),(1,0)の順で入力し たときの位相変化を示している。はじめに(1,1)を入力した とき、出力が得られないのは正常であるが、その後(1,0)を 入力すると、X5 の位相差が π/2 しか増加せず、出力が得 られていない。この原因を調べたところ、0-0-π SQUID の 非対称に起因し、周回電流の向きによって位相差が 0.06π 程度発生しており、スイッチに必要な電流が不足して動作 不良が起きていることが確認できた。

この問題は、バイアス電圧を増加させることで回避できるが、各 0-0-π SQUID の周回電流の向きの組合せ、即ち論理ゲートへの入力パターンの履歴によって動作マージンの下限が変わることを示唆している。講演では、今回実施したシミュレーション結果を含め、HFQ 論理ゲートについてより詳細な動作について議論を行う。

### <u>謝辞</u>

本研究は、JSPS 科研費(JP18H05211、JP23H05447、 22H01548)及びCREST(JPMJCR20C5)の支援を受けて実施 したものである。

## <u>参考文献</u>

- [1] F. Li et al., Supercond. Sci. Technol., 34, 025013, 2021.

- [2] 中山ほか, 応用物理学会春季学術講演会, 2023年3月.

- [3] Takeshita et al., Supercond. Sci. Technol., 36, 045004, 2023

Fig.1 Schematic diagram of HFQ XOR gate

Fig.2 XOR (Input1,Input2) = (1,0), (1,1)

Fig.3 XOR (Input1,Input2) = (1,1), (1,0)