# 単一磁束量子多数決論理ゲートを用いたバタフライ演算回路の設計

Design of a butterfly processing circuit using single flux quantum majority gate

横国大院理工¹ ○瀬川 亮輔¹, 山梨 裕希¹, 吉川 信行¹

Dept. of Electrical and Computer Eng., Yokohama Natl. Univ. 1

°Ryosuke Segawa<sup>1</sup>, Yuki Yamanashi<sup>1</sup>, Nobuyuki Yoshikawa<sup>1</sup>,

E-mail: segawa-ryosuke-nw@ynu.jp

#### 1. はじめに

本研究では、単一磁束量子回路(SFQ 回路)を用いた FFT (高速フーリエ変換)計算機の更なる低消費電力化・小型化を目標に、多数決論理ゲート(Majority ゲート)を使用したバタフライ演算回路(BPU)の設計を行った。

近年、社会の情報化が大きく進み、情報処理量が増大している。そこで、情報処理のさらなる高速化・低消費電力化が求められている。情報処理には半導体集積回路が使われることが主流であるが、微細化の限界や大きな消費電力の観点から、その代替となる技術の研究が必要である。そこで、超伝導回路の一種である SFQ 回路が注目されている。SFQ 回路は、Josephson 接合(JJ)を含んだ超伝導リングを並列に配置し、リング内の磁束の有無を「1」と「0」に対応させて演算を行う回路である。数十 GHz で高速動作し、消費電力も半導体集積回路の 0.1%程度という利点をもつ。

FFT は信号解析や画像解析に応用される。しかし、多量な演算が必要であり、消費電力や発熱量が問題となる。そこで、本研究では SFQ 回路の高速動作性、低消費電力性を利用して FFT 計算機の消費電力低減を目指した。

## 2. 多数決論理ゲートと加算器の設計

FFT 計算機は、バタフライ演算回路(BPU)が主要な部分を占める。BPU を繰り返し利用することで演算を行うため、BPU の低消費電力化・小型化が直接的に FFT 計算機の低消費電力化・小型化に繋がる。BPU は、先行研究においてシミュレーションで最高動作周波数 67 GHz、バイアスマージンは 50 GHz で 80 % - 125 %での動作が示されていた。

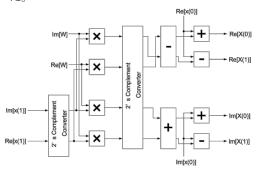

**Fig.1 Block Diagram of butterfly processing circuit** Data is input in parallel for the Twiddle factor and in serial for x(1).

**Fig.1** に BPU のブロック図を示す。BPU は乗算器 4 個、加算器 3 個、減算器 3 個で構成される。

我々はBPUの中でも最も消費電力・占有面積の大きい乗算器に着目し、乗算器の低消費電力化・小型化からBPU全体の低消費電力化・小型化を目指した。そこで、各乗算器内部の加算器(Bit Serial Adder)の改良を行った。

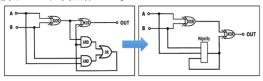

多数決論理ゲート(Majority ゲート)という新たな論理ゲートを設計することで、Fig.2 のように加算器を構成する論理ゲートの総数を5個から3個に削減した。多数決論理ゲートは3つの入力と1つの出力をもち、2つ以上SFQ入力があるとSFQが出力される、入力の多数決を取る論理ゲートである。多数決論理ゲートの利用により、先行研究で使用されていた加算器から消費電力を30%,面積を50%程度削減した。

**Fig.2** Comparison of bit serial adders Left: used in previous study, Right: newly proposed

## 3. バタフライ演算回路の設計

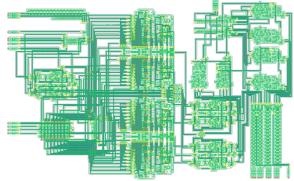

最後に、多数決論理ゲートを用いた加算器を組み込んだBPUを設計した。設計したBPUをFig.3に示す。加算器の改良により、先行研究のBPUから消費電力を10%程度、面積を30%程度削減することができた。

Fig.3 Circuit schematic of new butterfly processing circuit

#### 4. 参考文献

- (1) H. Cong, M. Li and M. Pedram, "An 8-b Multiplier Using Single-Stage Full Adder Cell in Single-Flux-Quantum Circuit Technology," *IEEE Trans. Appl. Supercond.*, vol. 31, 1303110, 2021.

- (2) Y. Sakashita, et al., "50 GHz demonstration of an integertype butterfly processing circuit for an FFT processor using the 10 kA/cm² Nb process," IEICE Trans. on Electron., vol. E98.C, pp. 232–237, 2015.