Oral presentation | 13 Semiconductors: 13.5 Semiconductor devices/ Interconnect/ Integration technologies

**Wed. Sep 18, 2024 9:00 AM - 12:30 PM JST | Wed. Sep 18, 2024 12:00 AM - 3:30 AM UTC A23 (TOKI MESSE 2F)**

# [18a-A23-1~13] 13.5 Semiconductor devices/ Interconnect/ Integration technologies

Masumi Saitoh(Kioxia), Hidehiro Asai(AIST)

9:00 AM - 9:15 AM JST | 12:00 AM - 12:15 AM UTC [18a-A23-1]

Quantitative Understanding of Temperature Dependence of Sub-threshold Swing in Si MOSFETs at Cryogenic Temperatures

Min-soo Kang<sup>1</sup>, Kasidit Toprasertpong,<sup>1</sup>, Hiroshi Oka<sup>2</sup>, Takahiro Mori<sup>2</sup>, Mitsuru Takenaka<sup>1</sup>, ○ Schin-ichi Takagi<sup>1</sup> (1.The Univ. Tokyo, 2.AIST)

9:15 AM - 9:30 AM JST | 12:15 AM - 12:30 AM UTC

[18a-A23-2]

Negative Back Bias Effect of Cryogenic 200 nm SOI MOSFET

ORyusei Ri<sup>1</sup>, Takayuki Mori<sup>1</sup>, Kousuke Hatta<sup>1</sup>, Ryousuke Kobayashi<sup>1</sup>, Hiroshi Oka<sup>2</sup>, Takahiro Mori<sup>2</sup>, Jiro Ida<sup>1</sup> (1.Kanazawa Univ., 2.AIST)

◆ Presentation by Applicant for JSAP Young Scientists Presentation Award 9:30 AM - 9:45 AM JST | 12:30 AM - 12:45 AM UTC [18a-A23-3]

Understanding Large Vth Shift by Hot Carrier Injection at Cryogenic Temperatures O(D)Shunsuke Shitakata<sup>1,2</sup>, Hiroshi Oka<sup>1</sup>, Kimihiko Kato<sup>1</sup>, Takumi Inaba<sup>1</sup>, Shota Iizuka<sup>1</sup>, Hidehiro Asai<sup>1</sup>, Takahiro Mori<sup>1</sup> (1.AIST, 2.APPI, Keio)

9:45 AM - 10:00 AM JST | 12:45 AM - 1:00 AM UTC [18a-A23-4]

Measuring Variability and Random Telegraph Noise at Cryogenic Temperatures using Transistor Matrix Array

OTomoko Mizutani<sup>1</sup>, Kiyoshi Takeuchi<sup>1</sup>, Takuya Saraya<sup>1</sup>, Hiroshi Oka<sup>2</sup>, Takahiro Mori<sup>2</sup>, Masaharu Kobayashi<sup>1,3</sup>, Toshiro Hiramoto<sup>1</sup> (1.IIS, Univ. of Tokyo, 2.AIST, 3.d.lab, Univ. of Tokyo)

#### • English Presentation

10:00 AM - 10:15 AM JST | 1:00 AM - 1:15 AM UTC [18a-A23-5]

Precise Extraction of Effective Mobility in Si nMOSFETs at Cryogenic Temperatures Using Quasi-Static C-V Technique

O(M2)Yutong Chen<sup>1</sup>, Zhao Jin<sup>1</sup>, Xueyang Han<sup>1</sup>, Hiroshi Oka<sup>2</sup>, Takahiro Mori<sup>2</sup>, Kasidit Toprasertpong<sup>1</sup>, Mitsuru Takenaka<sup>1</sup>, Shinichi Takagi<sup>1</sup> (1.The Univ. of Tokyo, 2.AIST)

#### English Presentation

10:15 AM - 10:30 AM JST | 1:15 AM - 1:30 AM UTC

[18a-A23-6]

Influence of Channel Resistance on Split C-V Characteristics in MOSFETs and the Correction Based on a Transmission Model for Accurate Evaluation of Effective Mobility

O(M2)Zhao Jin<sup>1</sup>, Yutong Chen<sup>1</sup>, Xueyang Han<sup>1</sup>, Hiroshi Oka<sup>2</sup>, Takahiro Mori<sup>2</sup>, Kasidit Toprasertpong<sup>1</sup>, Mitsuru Takenaka<sup>1</sup>, Shinichi Takagi<sup>1</sup> (1.U. Tokyo, Eng., 2.AIST)

$\hfill \hfill \hfill$

[18a-A23-7]

Si two-dimensional-superlattice MOS transistor and effective-mass enhancement

O(M2)Yuto Sugimoto<sup>1</sup>, Hiro Akahori<sup>1</sup>, Kota Takeuchi<sup>1</sup>, Yuryo Tozawa<sup>1</sup>, Hiroaki Satoh<sup>1,2</sup>, Masahiro Hori<sup>1,2</sup>, Yukinori Ono<sup>1,2</sup> (1.Shizuoka Univ., 2.RIE Shizuoka Univ.)

11:00 AM - 11:15 AM JST | 2:00 AM - 2:15 AM UTC

[18a-A23-8]

First-principal calculations on valley splitting in Si quantum wells stressed in the [110] direction

OToshiaki Hayashi<sup>1</sup>, Hiroyuki Kageshima<sup>2</sup>, Jinichiro Noborisaka<sup>1</sup>, Katsuhiko Nishiguchi<sup>1</sup> (1.NTT BRL, 2.Shimane Univ.)

11:15 AM - 11:30 AM JST | 2:15 AM - 2:30 AM UTC

[18a-A23-9]

Direct observation of electron capture processes in amphoteric defect states achieved by charge pumping in individual defects at MOS interface (12) -Lattice relaxation (III)-

OToshiaki Tsuchiya<sup>1</sup>, Masahiro Hori<sup>1</sup>, Yukinori Ono<sup>1</sup> (1.Shizuoka Univ.)

11:30 AM - 11:45 AM JST | 2:30 AM - 2:45 AM UTC

[18a-A23-10]

Direct observation of electron capture processes in amphoteric defect states achieved by charge pumping in individual defects at MOS interface (13) -Effects of level depth-

OToshiaki Tsuchiya<sup>1</sup>, Masahiro Hori<sup>1</sup>, Yukinori Ono<sup>1</sup> (1.Shizuoka Univ.)

11:45 AM - 12:00 PM JST | 2:45 AM - 3:00 AM UTC

[18a-A23-11]

Large-scale Characterization of Double Quantum Dots in Isoelectronic-Trap-Assisted Tunnel Field-Effect Transistors

OYusuke Chiashi<sup>1</sup>, Takumi Inaba<sup>1</sup>, Yagishita Atsushi<sup>1</sup>, Makoto Kato<sup>1</sup>, Tomohiro Ishikawa<sup>1</sup>, Hiroshi Oka<sup>1</sup>, Kimihiko Kato<sup>1</sup>, Hidehiro Asai<sup>1</sup>, Minoru Ogura<sup>1</sup>, Takashi Nakayama<sup>1</sup>, Shota Iizuka<sup>1</sup>, Takahiro Mori<sup>1</sup> (1.AIST)

Presentation by Applicant for JSAP Young Scientists Presentation Award

12:00 PM - 12:15 PM JST | 3:00 AM - 3:15 AM UTC

[18a-A23-12]

Evaluation of magnetic field-dependent quantum capacitance in a p-type Si double quantum dot

O(M1)Riku Wada<sup>1</sup>, Raisei Mizokuchi<sup>1</sup>, Chihiro Kondo<sup>1</sup>, Ryuta Tsuchiya<sup>2</sup>, Toshiyuki Mine<sup>2</sup>, Digh Hisamoto<sup>2</sup>, Hiroyuki Mizuno<sup>2</sup>, Jun Yoneda<sup>1</sup>, Tetsuo Kodera<sup>1</sup> (1.Tokyo Tech, 2.R&D Group, Hitachi Ltd)

12:15 PM - 12:30 PM JST | 3:15 AM - 3:30 AM UTC

[18a-A23-13]

Comparison of electron and hole by a silicon PN single-charge pump

OGento Yamahata<sup>1</sup>, Akira Fujiwara<sup>1</sup> (1.NTT BRL)

#### Si MOSFET の SS 値の極低温領域における温度依存性の定量的理解

Quantitative Understanding of Temperature Dependence of Sub-threshold Swing in Si MOSFETs at Cryogenic Temperatures

東大院工,姜旼秀,トープラサートポン カシディット,岡 博史,森 貴洋,竹中 充,<sup>○</sup>高木 信一 Univ. Tokyo, Min-Soo Kang, Kasidit Toprasertpong, Hiroshi Oka, Takahiro Mori, Mitsuru Takenaka, <sup>°</sup>Shinichi Takagi

E-mail: takagi@ee.t.u-tokyo.ac.jp

【背景】4K 近傍の極低温での Si MOSFET の電気 特性の正確な理解は、量子コンピュータシステム の制御回路応用などの点で重要である。MOSFET の低電圧動作の観点から重要な電気特性である sub-threshold swing (SS)は、Boltzmann 極限の下で は温度に比例するが、十分低温では値が飽和する ことが、SinMOSFET に対して報告されており[1]、 mobile tail state とバンド端にピーク値をもって Gaussian 分布する immobile state を仮定することに よって、実験結果を定量的に再現できることが知 られている[2-4]が、pMOSFETのSS値の報告は少 なく、nMOSFET との定量的比較にも乏しい。本研 究では、基板濃度の異なる Si nMOSFET と pMOSFET の SS 値の温度依存性を系統的に評価す ると共に、両者を定量的に再現できる物理モデル の構築に成功したので、報告する。

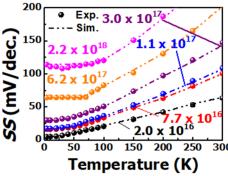

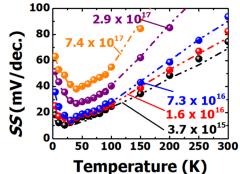

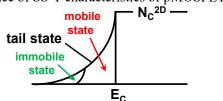

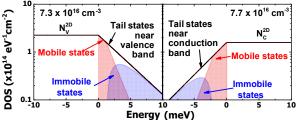

【実験手法・結果】10<sup>15</sup> 台から 10<sup>18</sup> cm<sup>-3</sup> 台までの 幅広い範囲での基板不純物濃度を持つ Si nMOSFET と pMOSFET の SS 値の温度依存性を Fig. 1 と 2 に示す。nMOSFET の SS 値は温度の低 下と共に飽和するが、pMOSFET の SS 値は温度の 低下と共に増加する傾向が見られることが分かる。 このような pMOSFET の SS の温度依存性と基板 不純物濃度依存性の実験結果は、従来の DOS モデ ル[1]では十分説明できないことから、アモルファ ス半導体の DOS モデルを念頭に、Fig. 3 に示す様 な tail state の深いエネルギー位置にある DOS を immobile state、浅いエネルギー位置にある DOS を mobile state と見なす新しいモデルを提案する。提 案モデルにより計算された SS 値の温度依存性を Fig.1 と 2 の破線で示す。実験結果をよく説明でき ることが分かる。同じ物理パラメータを用いて、 nMOSFET と pMOSFET の SS 値のドレイン電流依 存性も定量的に説明できる。これらの実験結果を 再現できる DOS のエネルギー分布を Fig. 4 に示 す。pMOSFET の方が immobile state の密度が高い ことから、温度の低下と共にフェルミレベルでの immobile state 量が、pMOSFET で著しく増加する。 これが pMOSFET の SS 値が温度の低下と共に増 加する物理的起源と考えられる。

【結論】SipMOSFETでは温度の低下と共にSS値が増大することを実験的に見出した。nMOSFETとの温度依存性の違いは、tail stateの低エネルギー領域を immobile state、高エネルギー領域を mobile state とする DOS モデルにより、定量的に再現できることが明らかとなった。

【謝辞】本研究は国立研究開発法人新エネルギー・ 産業技術総合開発機構(NEDO)の委託業務 (JPNP16007)の支援により実施した。 【参考文献】[1] Beckers et al., EDL, 41, 276 (2020) [2] Beckers et al., TED, 67, 1357 (2020) [3] Kang et al., JJAP, 61, SC1032 (2022) [4] Kang et al., JJAP, 62, SC1062 (2023)

Fig. 1 Experimental and simulated temperature dependence of SS-T characteristics of nMOSFETs

Fig. 2 Experimental and simulated temperature dependence of SS-T characteristics of pMOSFETs

Fig. 3 Newly proposed band tail state model including mobile states and immobile states.

Fig. 4 Comparison in simulated DOS distributions and boundary energy between mobile and immobile states between nMOSFETs and pMOSFETs with similar N<sub>sub</sub> of (7-8) x 10<sup>16</sup> cm<sup>-3</sup>

## 低温下おける 200 nm SOI MOSFET の負基板バイアス依存性

Negative Back Bias Effect of Cryogenic 200 nm SOI MOSFET

金沢工大<sup>1</sup>, 産総研<sup>2</sup>, <sup>o</sup>李 龍聖<sup>1</sup>, 森 貴之<sup>1</sup>, 八田 浩輔<sup>1</sup>, 小林 亮介<sup>1</sup>, 岡 博史<sup>2</sup>, 森 貴洋<sup>2</sup>, 井田 次郎<sup>1</sup> Kanazawa Inst. of Tech.<sup>1</sup>, AIST<sup>2</sup>, <sup>o</sup>R. Ri<sup>1</sup>, T. Mori<sup>1</sup>, K. Hatta<sup>1</sup>, R. Kobayashi<sup>1</sup>, H. Oka<sup>2</sup>, T. Mori<sup>2</sup>, J. Ida<sup>1</sup> E-mail: c6300973@st.kanazawa-it.ac.jp

<u>はじめに</u>: 量子コンピュータの量子ビット数を増やすためには配線数の増大及びそこからの熱流入が課題であり、解決のために Cryo-CMOS 技術の研究開発が行われている. MOSFET の中でも、SOI 技術は基板バイアス( $V_{sub}$ )によってしきい値電圧( $V_{th}$ )を制御することが可能であり、低消費電力 Cryo-CMOS の実現が期待できる. その意味で  $V_{th}$  を低くできる正基板バイアスをまず評価し極低温でのみ現われるヒステリシス現象を見出し報告してきた[1]. 本稿では  $V_{th}$  を高くする方向である負基板バイアスの温度依存性においても、低温と室温では異なる振舞いを示すことが判明したので報告する.

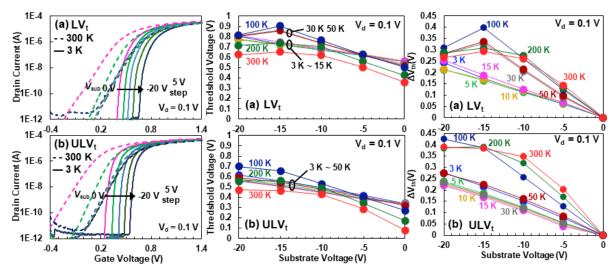

実験方法及び結果: 実験にはゲート長 200 nm, ゲート幅 1  $\mu$ m, ゲート酸化膜厚 4.4 nm, Si 膜厚 40 nm, 埋め込み酸化膜厚 145 nm のラピスセミコンダクタ社 200 nm SOI プロセス によって作製された MOSFET を使用した.チャネル不純物濃度を変えたデバイスを作製し、本稿では Low Vt (LVt)及び、より不純物濃度が低い Ultra Low Vt (ULVt)の結果を示す. Fig. 1 に 300 K 及び 3 K における  $I_d$ – $V_g$ 特性の  $V_{sub}$  依存性を示す. (a)は LVt、(b)は ULVt である(Fig. 2, 3 も同様). Fig. 2 に  $V_{th}$ – $V_{sub}$  の温度依存性を示す. Fig. 3 に  $V_{sub}$  = 0 V が基準の  $V_{sub}$  に対する  $V_{th}$  の変化量( $\Delta V_{th}$ )を示す. LVt と ULVt のどちらのデバイスも 300 K から 200 K までは、 $V_{sub}$  増加とともに  $V_{th}$  の変化が飽和する Bulk-MOSFET と同等な基板バイアス特性を示すが、100 K から 30K で直線的になり、さらに低温では直線的で変化量が小さくなることが確認できる. 具体的には、Fig. 2(a)より、300 K から 30 K では、 $V_{sub}$  = -15 V ほどで  $V_{th}$  が飽和するのに対して、 $V_{th}$  が増加している. Fig. 2(b)でも同じように 100 K まで飽和が見えるが、50 K から  $V_{sub}$  に比例して  $V_{th}$  が増加していることが確認できる.これは、温度によるフリーズアウトの影響、完全空乏、部分空乏の程度の差などが考えられる.

<u>謝辞:</u> 本講演で発表した研究は、国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO) の委託業務 (JPNP16007)の結果得られたものです.

参考文献: R.Ri et al., "Back Bias Effect with Hysteresis in Cryogenic 200 nm SOI MOSFETs", EuroSOI-ULIS, May. 2024

Fig. 1  $I_d$ – $V_g$  dependence on  $V_{sub}$ . (a) ULV<sub>t</sub>, (b) LV<sub>t</sub>. --- 300 K — 3 K

Fig. 2  $V_{\text{th}}$  dependence on  $V_{\text{sub}}$ . (a) ULV<sub>t</sub>, (b) LV<sub>t</sub>.

Fig. 3  $\Delta V_{\text{th}}$  dependence on  $V_{\text{sub}}$ . (a) ULV<sub>t</sub>, (b) LV<sub>t</sub>. (based on  $V_{\text{sub}} = 0$  V).

# 極低温下でのホットキャリア注入に起因した巨大なしきい値電圧変動の理解

Understanding Large V<sub>th</sub> Shift by Hot Carrier Injection at Cryogenic Temperatures 產総研¹, 慶大物情² <sup>O</sup>(D) 下方駿佑¹², 岡博史¹, 加藤公彦¹, 稲葉エ¹, 飯塚将太¹, 浅井栄大¹, 森貴洋¹ AIST¹, APPI, Keio², °S. Shitakata¹², H. Oka¹, K. Kato¹, T. Inaba¹, S. Iizuka¹, H. Asai¹, and T. Mori¹ E-mail: s-shitakata@aist.go.jp

大規模量子コンピュータの実現には、室温からの熱流入を削減しながら量子ビットの状態の制御・読出を行うクライオ CMOS 集積回路技術が不可欠である。MOSFET の極低温動作の理解が求められるが、近年の研究では、しきい値電圧( $V_{th}$ )の温度依存他の様々な特性にバンド端準位が強く影響することが明らかになってきた[1,2]。一方で、信頼性に関連する議論は始まったばかりであり、これまでにはホットキャリアによる特性劣化(Hot Carrier Degradation; HCD)が低温で増大することが報告されているが[3]、そのメカニズムは明らかではない。そこで本研究では、ホットキャリア注入後の $V_{th}$ 変動の温度依存性を評価し、また極低温下では有効性が未検証である重水素( $D_2$ )アニールによる劣化抑制効果[4]を試験することで、メカニズムの理解を試みた。実験には、(100)面がルクシリコンウエハ(10) 型、100 型、

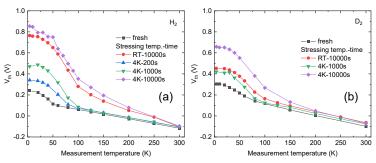

実験には、(100)面バルクシリコンウエハ(p 型、 $1\sim5\Omega$ cm)に poly-Si/熱酸化 SiO<sub>2</sub> ゲートスタックのセルフアラインプロセスで作製した n-MOSFET を用いた。酸化膜厚は 8nm である。電極形成後に水素 $(H_2)$ または  $D_2$  フォーミングガスアニール(FGA)をそれぞれ 400 で 30 分間行った。作製した試料(f 一ト長  $1\mu$ m)に対して、室温または 4K でのホットキャリアストレス印加 $(V_D, stress=6.5V, V_G, stress=2.3V)$ を行った。その後各温度でストレス印加した試料について、温度 $(T_m)$ を変化させ電気特性の評価を行った(図 1)。

まず  $H_2$  FGA 試料について、4K でのストレス印加後は、既報告[3]にあるような大きな  $V_{th}$  変動が観測された。ストレス印加時間( $I_{tress}$ )であっても、室温に戻すと  $V_{th}$  の変化量は微少になっていることがわかる(紫線)。 一方、室温でのストレス印加時間( $I_{tress}$ )であっても、室温に戻すと  $V_{th}$  の変化量は微少になっていることがわかる(紫線)。 一方、室温でのストレス印加試別についても同様に  $V_{th}$  温度依存性をみると、ほぼ同一の傾向を示している(赤線)。このことから、ストレス印加温度に関わらず、同一描像の界面劣化が発生していると考えられる。一方で、 $V_{th}$  に与える影響は、ストレス印加温度によって異なることが示唆される。ここで得られた  $V_{th}$  で加温度依存性であり、バンド端準位密度に依存すると考えられている[1,2]。この  $V_{th}$  の上昇量はストレス印加時間に相関する(青線、緑線、紫線)ことから、極低温下で見られる巨大な  $V_{th}$  変動は、バンド端準位の増加に起因すると考えられる。こで注目すべきは、今回のストレス時間は、印加温度によらず、室温では I0mV 以下の微少な  $V_{th}$  変動しか起こさない時間であるということである。それにも関わらず、4K では I00mV 以上の巨大な  $V_{th}$  変動が発生している。室温における I(th) 出力らず、I(th) を動が発生している。を室温における I(th) は I(th) でが I(th) であるとが I(th) であるとが I(th) での I(th) である。それとはまるで独立するように I(th) では I(th) の増加に起因すると考えられているが I(th) に記しているものと考えられるバンド端準位量の増大は、界面ダングリングボンド欠陥量の増大以上に発生しているものと考えられるが、I(th) で I(th) で I

以上まとめると、HCD による極低温下での  $V_{th}$  増大現象は、バンド端準位の増加が原因であることがわかった。これは、HCD によるダングリングボンドの発生量とは比例していないと考えられる。一般に HCD を抑制する  $D_2$  アニールは、AK ストレス印加においては効果が薄く、これはフォノン周波数の温度依存に起因すると考えられる。

【謝辞】本研究は NEDO の委託業務(JPNP16007)および文部科学省 Q-LEAP(JPMXS0118069228)の助成を受けて実施した研究の結果得られたものである。本研究におけるデバイス試作は、産業技術総合研究所・未踏デバイス試作共用ライン(COLOMODE)にて実施された

【参考文献】 [1] A. Beckers et al., IEEE-JEDS 8, 780 (2020). [2] H. Oka et al., IEDM 2023. [3] Y. Zhang et al., IEEE-TDMR 21, 620 (2021). [4] J. W. Lyding et al., APL 68, 2526 (1996). [5] C. G. Van de Walle and W. B. Jackson, APL 69, 2441 (1996).

Fig. 1 Experimental procedure of this study.

Fig. 2 V<sub>th</sub> as a function of measurement temperature under different stress condition (temperature and time) for (a) H<sub>2</sub> FGA and (b) D<sub>2</sub> FGA.

# トランジスタマトリックスアレイを用いた 極低温における特性ばらつきとランダムテレグラフノイズの測定

Measuring Variability and Random Telegraph Noise

at Cryogenic Temperatures using Transistor Matrix Array

東大生研<sup>1</sup>, 産総研<sup>2</sup>, 東大 d.lab<sup>3</sup> O水谷 朋子<sup>1</sup>, 竹内 潔<sup>1</sup>, 更屋 拓哉<sup>1</sup>, 岡 博史<sup>2</sup>, 森 貴洋<sup>2</sup>, 小林 正治<sup>1,3</sup>, 平本 俊郎<sup>1</sup>

<sup>1</sup>IIS, Univ. of Tokyo, <sup>2</sup>AIST, <sup>3</sup>d.lab, Univ. of Tokyo <sup>O</sup>Tomoko Mizutani<sup>1</sup>, Kiyoshi Takeuchi<sup>1</sup>, Takuya Saraya<sup>1</sup>, Hiroshi Oka<sup>2</sup>, Takahiro Mori<sup>2</sup>, Masaharu Kobayashi<sup>1,3</sup>, and Toshiro Hiramoto<sup>1</sup> E-mail: mizutani@ nano.iis.u-tokyo.ac.jp

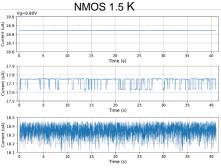

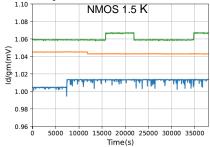

【はじめに】量子コンピュータを実用化には,極低温で動作 する CMOS 回路が不可欠であり, 回路設計には Cryo-CMOS の特性ばらつきを理解する必要がある[1-7]. 本研究では,極 低温測定用のトランジスタマトリックスアレイを作製し, Cryo-CMOS の特性ばらつきおよびランダムテレグラフノイ ズ (RTN) を調査したので報告する[8]. 【結果】65nm バル ク技術で作製したトランジスタマトリクスアレイを用い て, nMOS, pMOS の 300 K および 1.5 K における IV 特性を 測定した. 図 1 は定電流 (0.1μA×W/L) および外挿法 (それ ぞれ V<sub>THC</sub>, V<sub>THEX</sub> と表記) によって抽出されたしきい値電圧 (V<sub>TH</sub>) の正規確率プロットである. L/W=65nm/120nm であ る.  $1.5 \, \mathrm{K}$  では  $\mathrm{V}_{\mathrm{TH}}$  ばらつきが増加する. また  $\mathrm{V}_{\mathrm{THC}}$  は  $\mathrm{V}_{\mathrm{THEX}}$ よりもばらつきが大きい. これらは以前 nMOS について報 告した結果と一致しており[3], 今回 pMOS においても確認 された. 本研究では Cryo-CMOS の RTN ばらつきについて も調査した. ノイズ波形はデバイス間で大きく異なるため, ノイズ動作を理解するには多数のデバイスの RTN 測定が不 可欠である. 図 2 は 1.5K における nMOS の RTN 波形の例で ある. ノイズ波形にはばらつきがあることがわかる. また疑 似並列測定法[9]を用いて,室温で報告されている時定数が非 常に長い RTN が極低温においても多数存在することを確認 した (図3). 【まとめ】極低温測定用のトランジスタマトリ ックスアレイを作製し、1.5 K での静特性およびノイズ特性 のばらつき測定を行った. 疑似並列測定法を用いたノイズ測 定では 1.5K で極めて遅い RTN の存在を確認した.

【謝辞】本講演の成果は、国立研究開発法人新エネルギー・ 産業技術総合開発機構 (NEDO) の委託業務 (JPNP16007) の結果得られたものです.

【文献】 [1] A. Appaswamya el al., IEEE ISDRS, 2009. [2] N. C. Dao et al., IEEE EDL, vol. 38, no. 7, pp. 847-850, 2017. [3] T. Mizutani et al., JJAP, 61, SC1006, 2022. [4] K. D., Torsten et al., Cryogenics, vol. 62, pp. 84-93, 2014. [5] B. C. Paz et al., IEEE ICMTS, 2020, 8.3. [6] A. Grill et al., IEEE IRPS, 2020. [7] P. A. T. Hart et al., IEEE J-EDS, Vol. 8, pp. 797-806, 2020.Cryogenics, vol. 62, pp. 84-93, 2014. [8] T. Mizutani et al., IEEE ICMTS, 2024. [9] K. Takeuchi et al., IEEE VLSI Tech. 2009, pp. 54-55.

Fig.1. Cumulative distributions of V<sub>THC</sub> and V<sub>THEX</sub>. (a) nMOS and (b) pMOS.

Fig.2. Drain current vs. time waveforms of three identically designed FETs to show variability of noise.

Fig.3. RTN waveforms with extremely slow transitions.

#### Precise Extraction of Effective Mobility in Si nMOSFETs at Cryogenic Temperatures Using Quasi-Static C-V Technique

Yutong Chen<sup>1</sup>, Zhao Jin<sup>1</sup>, Xueyang Han<sup>1</sup>, Hiroshi Oka<sup>2</sup>, Takahiro Mori<sup>2</sup>, Kasidit Toprasertpong<sup>1</sup>, Mitsuru Takenaka<sup>1</sup> and Shinichi Takagi<sup>1</sup>

The University of Tokyo, Faculty of Engineering<sup>1</sup>, National Institute of Advanced Industrial Science and Technology<sup>2</sup>

E-mail: chenyutong@mosfet.t.u-tokyo.ac.jp

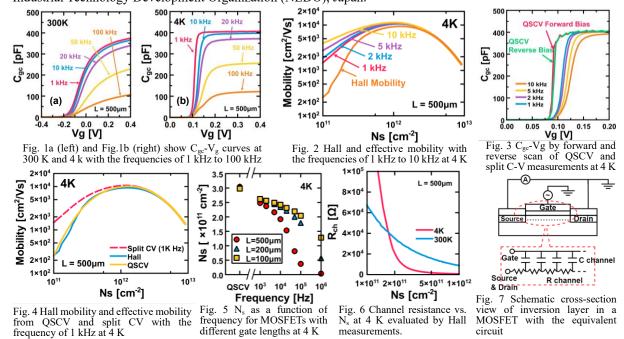

[Background] The increasing demand for the development of quantum computers and control circuits of qubits has led to a focus on cryogenic CMOS [1]. Consequently, it is important to examine the electrical characteristics of CMOS at cryogenic temperatures. One of the important parameters for I-V characteristics is the inversion-layer mobility, which can be measured in several ways, such as Hall measurements and effective mobility based on extraction of surface carrier concentration (N<sub>s</sub>) made by split C-V [2]. However, the accuracy of effective mobility as evaluated by split C-V at low temperatures has not yet been examined. In this study, we investigate this issue quantitatively by varying the measurement frequency. Our findings indicate that the conventional split C-V approach may not be universally applicable to long channel MOSFETs, because of the channel resistance. Consequently, we introduce the Quasi Static C-V (QSCV) method [3, 4] to accurately determine Ns even at 4 K. **[Experiment]** I-V transfer measurements and split C-V measurements are performed from 300 K to 4 K on n-MOSFETs with gate length (L)/width (W) of  $500\,\mu\text{m}/160\,\mu\text{m}$ ,  $200\,\mu\text{m}/200\,\mu\text{m}$ , and  $100\,\mu\text{m}/100\,\mu\text{m}$ . All devices are made on (100) Si wafer with a substrate boron concentration of  $3\times10^{16}/\text{cm}^{-3}$  and  $6.8\,\text{nm}$  gate oxide (SiO<sub>2</sub>) thickness. In addition, we performed Hall measurements from 300 K to 4 K with the magnetic field strength of 1T for the nMOSFETs with gate length/width of 500 μm/160 μm.

[Results] Figs. 1a and 1b show the gate channel capacitance (C<sub>gc</sub>)-V<sub>g</sub> characteristics for nMOSFETs with 500 μm/160 μm by using split C-V method with different frequencies in a temperature range of 300 K and 4 K, respectively. It is evident that frequency dispersion is observed at both temperatures, with the phenomenon being more pronounced at 4 K. Fig. 2 presents a comparison between Hall mobility and effective mobility, evaluated at various frequencies from 1 kHz to 10 kHz at 4 K. In low N<sub>s</sub> region, the measured effective mobility is much higher than the Hall mobility. Fig. 3 shows the  $C_{gc}$ - $V_g$  characteristics by using QSCV and split C-V at 4 K. Fig. 4 shows the comparison between Hall mobility and effective mobilities measured by split C-V and QSCV at 4 K. The effective mobility obtained by QSCV is in good agreement with the Hall mobility, thereby demonstrating the high accuracy of the Ns and mobility evaluated by QSCV at cryogenic temperatures. Fig. 5 shows N<sub>s</sub> as a function of frequency at 4 K measured from nMOSFETs with different gate lengths. The results indicate that the nMOSFET with longer channel length causes the larger reduction in Ns at 4 K. Fig. 6 shows channel resistance versus N<sub>s</sub> at 300 K and 4 K, calculated from Hall measurements by using  $R_{ch} = 1/(\mu_H e N_S)$ . It is observed in Fig. 7 that the long channel device at cryogenic temperature shows the significantly higher channel resistance in the low N<sub>s</sub> region than that at room temperature because of the lower mobility, leading to inaccuracy of N<sub>s</sub> by split C-V at cryogenic temperature.

[Conclusion] We have proposed a QSCV method to extract Ns and effective mobility in a low Ns region. This method differs from the conventional split C-V method in that it is experimentally demonstrated to be more accurate by comparison with Hall mobility.

[1] E. Charbon *et al*, IEDM, 13.5 (2016) [2] J. Koomen, Solid-State Electron., 16, 801 (1973) [3] K. Toprasertpong et al, IEDM, 23.7 (2019) [4] K. Sumita et al, Appl. Phys. Lett. 119, 103501 (2021)

[Acknowledgments] This work was supported by a project, JPNP16007, commissioned by the New Energy and Industrial Technology Development Organization (NEDO), Japan.

measurements.

circuit

different gate lengths at 4 K

# Influence of Channel Resistance on Split C-V Characteristics in MOSFETs and the Correction Based on a Transmission Model for Accurate Evaluation of Effective Mobility

Zhao Jin<sup>1</sup>, Yutong Chen<sup>1</sup>, Xueyang Han<sup>1</sup>, Hiroshi Oka<sup>2</sup>, Takahiro Mori<sup>2</sup>, Kasidit Toprasertpong<sup>1</sup>, Mitsuru Takenaka<sup>1</sup> and Shinichi Takagi<sup>1</sup>

The University of Tokyo, Faculty of Engineering<sup>1</sup>, National Institute of Advanced Industrial Science and Technology<sup>2</sup>

E-mail: jin@mosfet.t.u-tokyo.ac.jp

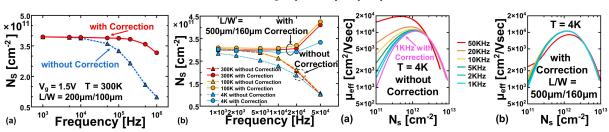

**[Background]** Split C-V is a classic technique for evaluating the electrical properties of MOSFET devices. Specifically, it involves measuring the gate-channel capacitance ( $C_{ge}$ ) to estimate surface carrier density ( $N_{S}$ ) and effective carrier mobility [1]. This technique is particularly valuable for FETs on insulating substrates, where traditional bulk MOS capacitor structures are unavailable [2, 3, 4]. Traditionally, the impact of channel resistance is neglected by choosing a sufficiently low measurement frequency. However, high MOS channel resistance due to low  $N_{S}$ , long channel length, and low mobility can degrade the accuracy of  $C_{ge}$  measurements and the subsequent evaluation of  $N_{S}$  and effective mobility [5]. When there is limitation to lowering the measurement frequency, a method to eliminate the influence of channel resistance on  $C_{ge}$  is very important. In this study, we propose and demonstrate a  $C_{ge}$  correction method by using a transmission model for MOS channels.

**[Experiments]** Fig. 1 illustrates the measurement setup for split C-V and the transmission line equivalent circuit model of a MOSFET. This model includes the differential capacitance and resistance along the channel length of a MOSFET [5]. In practical measurements, a phase change occurs due to the delay caused by RC circuits, which affects the accuracy of  $C_{gc}$  measurements [5]. Fig. 2 presents examples of the calculated discrepancy between the measurable capacitance and the correct  $C_{gc}$  as a function of measurement frequency. The discrepancy increases with higher frequencies and appears at lower frequencies for higher channel resistance and gate oxide capacitance. Using a transmission line model, the relationship between measured parallel capacitance  $C_{measure}$ , conductance  $G_{measure}$ , and  $G_{gc}$  are expressed as a function of measurement frequency ω, as seen in Table 1. The corrected  $G_{gc}$  is evaluated as a function of ω by using a parameter τ, which can be determined by experimental  $G_{measure}$  and  $G_{measure}$  are the following parameter  $\sigma$ , which can be determined by experimental  $G_{measure}$  and  $G_{measure}$  and  $G_{measure}$  and  $G_{measure}$  and  $G_{measure}$  and  $G_{measure}$  are the following parameter  $\sigma$  and  $G_{measure}$  and  $G_{measure}$  are the following parameter  $\sigma$  and  $G_{measure}$  are the following parameter  $\sigma$  and  $G_{measure}$  and  $G_{measure}$  are the following parameter  $\sigma$  and  $G_{$

**[Results]** Fig. 3(a) shows the original and corrected  $N_S$  at a given  $V_g$ . The variation in  $N_S$  with different frequencies is significantly reduced after applying the correction. Fig. 3(b) depicts the estimated  $N_S$  at a given  $V_g$  as a function of frequency at various temperatures. At 4 K, the change in  $N_S$  is more substantial. However, the proposed method effectively corrects  $N_S$  even at this temperature. Fig. 5 illustrates the effective mobility determined from  $N_S$  with and without correction at 4 K at different frequencies. Without correction, the mobility for  $N_S$  below  $10^{12}$  cm<sup>-2</sup> is strongly dependent on the measurement frequency due to inaccuracies in estimated  $N_S$ . The correction method provides consistent and accurate effective mobility values until the measurement frequency of 20 kHz.

**[Conclusion]** We proposed a method to correct the split C-V characteristics and have verified the effectiveness through experiments. Accuracy in effective mobility evaluation can be significantly improved for MOSFETs with high channel resistance by using this method.

[References] [1] C. G. Sodini et al, Solid-State Electron., 25 (1982) 833 [2] M. Schmidt et al, Solid-State Electron., 53 (2009) 1246 [3] H. Oka et al, VLSI Tech. & Circ. (2022) [4] I. Nifa et al, Microelectron. Eng. 215 (2019) 110976 334 [5] P. Chow et al, IEEE TED, 33 (1986) 1299

[Acknowledgments] This work was supported by a project, JPNP16007, commissioned by the New Energy and Industrial Technology Development Organization (NEDO), Japan.

Fig. 1 Measurement setup of split C-V and equivalent circuit [5] of in-version-layer of a MOSFET

Table 1 Relationship between measured  $C_{measure}$ ,  $G_{measure}$ , and  $C_{gc}$  expressed by frequency  $\omega$

Fig. 2 Calculated measurable Cgc versus frequency

Fig. 3 Change in evaluated  $N_S$  at certain gate voltage with and without correction as a function of measurement frequency at different temperatures

Fig. 4 Effective mobility calculated from split C-V with and without correction at 4 K

# シリコン2次元超格子 MOS トランジスタの提案と有効質量増大の観測

Si two-dimensional-superlattice MOS transistor and effective-mass enhancement

静大院工<sup>1</sup>, 静大電研<sup>2</sup> <sup>O</sup>(M2)杉本 裕人<sup>1</sup>, 赤堀 海洋<sup>1</sup>, 竹内 滉太<sup>1</sup>, 戸澤 佑亮<sup>1</sup>, 佐藤 弘明<sup>1,2</sup>, 堀 匡寛<sup>1,2</sup>, 小野 行徳<sup>1,2</sup>

Shizuoka Univ., °Yuto Sugimoto, Hiro Akahori, Kota Takeuchi, Yuryo Tozawa, Hiroaki Satoh, Masahiro Hori, Yukinori Ono

E-mail: sugimoto.yuto.19@shizuoka.ac.jp

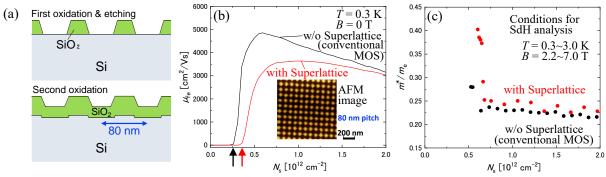

【はじめに】 2次元超格子構造は、2次元電子系のバンド変調(分散関係の変調)を誘起し、これにより電子相関が増強され、超伝導などの新奇物性を発現させることができる。このためグラフェンなどの2次元層状物質[1]や GaAs ヘテロ構造[2]において活発に研究がなされているが、Si を用いた検討はなされていない。ここでは、MOS(SiO $_2$ /Si 界面)チャネル電子系の超伝導化の可能性を探索することを目的に、MOS 界面における強相関電子系の生成を目指して、「2次元超格子MOSトランジスタ」とその作製プロセスを提案する。また、実際に試作し、低温( $T=0.3\sim3.0$  K)において、強い電子相関の生成に必須となる、有効質量の顕著な増大を観測したので報告する。

【2次元超格子構造とその作製プロセス】2次元超格子構造は、ゲート熱酸化プロセスを2段階に分けることにより形成する。第一段の熱酸化により形成した酸化膜上に電子線描画を用いてレジストの2次元配列パターンを形成し、続いてこれをマスクに HF ウエットエッチングにより部分的に酸化膜を除去する (Fig. 1(a) top)。その後、追酸化を行い酸化膜厚に周期的なアンデュレーションを生じさせる (Fig. 1(a) bottom)。同構造においては、酸化膜厚の薄い領域に電界が集中し、ゲート電圧印加により2次元チャネルの電子密度に空間的な濃淡パターンが生じると期待される。実際の試作には SOI 基板 ((100)面)を用い、80 nm ピッチの正方2次元周期構造を形成した (Fig. 1(b)の AFM 像参照)。第一段、第二段の熱酸化膜の膜厚は、ともに15 nm に設定した。

【測定結果とその意義】ここでは、電界効果移動度( $\mu_{fe}$ )と有効質量( $m^*$ )のチャネル電子密度( $N_s$ )依存性を計測し、2次元パターンのない通常 MOS トランジスタとの比較を行った。 $\mu_{fe}$  はゼロ磁場での伝導度計測により求め、一方、 $m^*$ と $N_s$ は、Shubnikov-de Haas(SdH)振動を解析することにより求めた[1,3]。Fig. 1(b)は、T=0.3 K における $\mu_{fe}$ の  $N_s$  依存性を示している。2次元超格子構造を有する場合、低  $N_s$  側で $\mu_{fe}$  が低く抑えられており、特に矢印で示されているように $\mu_{fe}$  の立ち上がりを与える  $N_s$  が増大している。これは、2次元電子系が金属絶縁体転移する際の臨界電子密度の増大を反映しているものと予想され、電子相関の影響が強く示唆される。Fig. 1(c)は、有効質量比  $m^*/m_e$ ( $m_e$  は真空中での電子質量)の  $N_s$  依存性を示している。2次元超格子構造を有する場合、低  $N_s$  側で  $m^*/m_e$  が急激にかつ大幅に増大している。有効質量の増大は、伝導帯電子のバンドの曲率の低下を意味しており、そのような場合、運動エネルギーに打ち勝って電子相関(電子間相互作用)が強く働くことが知られている[4]。ここでの有効質量増大の観測は、そのような強相関電子系をシリコン MOS トランジスタ上で実現できる可能性を示している。

本研究は、科研費(22K18294, 24H00312, 24K00942)の助成を受けて行われた。

- [1] Y. Cao et al., *Nature* **556** (2018) 80. [2] D. Q. Wang et al., *Nano Lett.* **23** (2023) 1705.

- [3] F. F. Fang et al., PRB 16 (1977) 4446. [4] A. A. Shashkin and S. V. Kravchenko, Appl. Sci. 9 (2019) 1169.

Fig. 1: (a) Process for the two-dimensional superlattice. (b) Field-effect mobility  $\mu_{\text{fe}}$  as a function of the electron density  $N_s$ . The arrows correspond to the threshold voltages, reflecting the critical densities of the metal-insulator transition. Inset shows the AFM image of the superlattice. (c) Effective mass ratio  $m^*/m_e$  as a function of  $N_s$ , derived using SdH oscillations.

# [110]方向に応力がかかった Si 量子井戸における谷分離の第一原理計算

First-principal calculations on valley splitting in Si quantum wells stressed in the [110] direction NTT 物性研 <sup>1</sup>, 島根大学 <sup>2</sup> O林 稔晶 <sup>1</sup>, 影島 博之 <sup>2</sup>, 登坂 仁一郎 <sup>1</sup>, 西口 克彦 <sup>1</sup>

NTT BRL <sup>1</sup>, Shimane Univ. <sup>2</sup>, °Toshiaki Hayashi<sup>1</sup>, Hiroyuki Kageshima<sup>2</sup>, Jinichiro Noborisaka<sup>2</sup>,

#### Katsuhiko Nishiguchi<sup>2</sup>

#### E-mail: tshk.hayashi@ntt.com

Si 閉じ込め構造における谷分離の研究は量子ビットのデコヒーレンスを誘発する原因の一つとして近年注目を浴びている[1,2]。通常、Si-MOS や量子ドットデバイスにおける谷分離の大きさは1meV 以下と小さい。それに対し、我々のグループは SIMOX 基板の Si/埋め込み酸化膜界面において約 23meV と非常に大きい谷分離を発見してきた[3]。これは Si ベース量子ビットのデコヒーレンス抑制につながるかもしれない。しかし、Si/埋め込み酸化膜界面で何が起こっているかを実験的にアクセスすることが難しく、巨大谷分離の起源は長年謎のままだった。我々のデバイスは高温熱処理をおこなった特殊なものであるということを踏まえ、Si/埋め込み酸化膜界面に大きな歪が生じ、その結果として谷分離が増大するという仮説を立て、実験結果の再解釈を実施した[4]。

我々は実験と並行して Si 量子井戸の第一原理計算を実施している[5]。特に今回の発表では [110]方向に応力が印加された場合について議論する。プログラムは PHASE を用いている。計算 モデルは (001)面に平行な Si スラブで、両面とも H 原子で終端してある。歪テンソルを用いて応

図 1. 谷分離の応力依存性

力を歪に変換[6]し、[110]、[110]、[001]方向にとった基本格子ベクトルの長さを調節することによって歪んだ格子をモデル化した。図 1 は 21 原子層の Si スラブにおける谷分離を応力の関数としてプロットしている。低圧力では量子閉じ込めによる谷分離が支配的であるが、応力が強くなるにつれ谷分離はその強度に比例する。これは大川の kp 法による解析結果[7]を再現している。以上から、電界による閉じ込め効果[5]と歪の効果を組み合わせれば、我々が実験的に示した巨大谷分離を再現できる可能性を示せた。

- [1] M. Lodari, et al., Phys. Rev. Lett. 128, 176603 (2022).

- [2] G. Wang, et al., Phys. Rev. B 105, 165308 (2022).

- [3] K. Takashina, et al., Phys. Rev. Lett. 96, 236801 (2006).

- [4] J. Noborisaka, et al., J. Appl. Phys. 135, 204302 (2024).

- [5] 林、影島、登坂、西口、第84回応用物理学会 秋季学術講演会 21a-A304-7.

- [6] V. Sverdlov, "Strain-Induced Effects in Advanced MOSFETs", Springer-Verlag (2011).

- [7] F. J. Ohkawa and W. Uemura, J. Phys. Soc. Jpn. 43, 917 (1977).

# MOS 界面の単一欠陥チャージポンピングによって可能となった 両性準位における電子捕獲素過程の直接観測 (12) -欠陥構造緩和(Ⅲ)-

Direct observation of electron capture processes in amphoteric defect states achieved by charge pumping in individual defects at MOS interface (12) -Lattice relaxation (III)-

静大電研 <sup>○</sup>土屋敏章, 堀 匡寬, 小野行徳

Shizuoka Univ., <sup>O</sup>Toshiaki Tsuchiya, Masahiro Hori, Yukinori Ono E-mail: tsuchiya.toshiaki@shizuoka.ac.jp

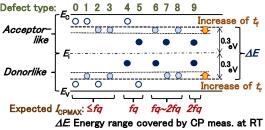

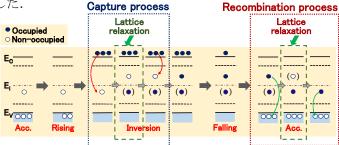

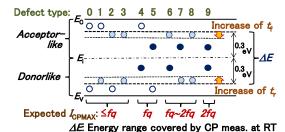

これまで我々はチャージポンピング(CP)法によってナノ MOS 素子内に存在する MOS 界面欠陥の単一性の判定法を確立し、単一欠陥からの CP 電流  $I_{CPS}$  が  $0\sim 2fq$ (f:ゲートパルス周波数、g:電気素量)の様々な値を示すことを発見した[1]. これにより単一欠陥が 2 電子準位を有していることを実証し、すべての  $I_{CPS}$  値を説明できる単一欠陥の 10 種のタイプ分類を行った(図 1). また、 $I_{CPS}=fq$  一定を大前提としている従来 CP 理論を本質的に改訂した[2]. さらに、単一界面欠陥の 2 電子準位の密度分布(DOS)を導出し、既報[3]の ESR による  $P_{b0}$  センターの DOS との一致性を示した。そして、各準位における伝導帯電子の捕獲時定数の実測[4]、および、各準位に捕獲された電子の価電子帯ホールとの再結合時定数の実測に成功し[5]、これらの値を考察してこの 2 電子準位がドナー型(D-like)とアクセプタ型(A-like)の両性を有することに整合することを実証した。以上の結果から、界面欠陥が  $P_{b0}$  セン

ターであることを単一欠陥単位(原子スケール)ではじめて実証した。さらに、D-like および A-like 準位への連続的な伝導帯電子捕獲素過程の観測から、D-like 準位が電子捕獲した直後に欠陥構造緩和が起きていることの直接観測に成功した[6][7]。また、両準位に捕獲されている電子が価電子帯ホールと連続的に再結合する素過程の観測から、A-like 準位の捕獲電子が再結合した直後に欠陥構造緩和が起きていることの直接観測に成功した[8]。さらに、電子捕獲過程における欠陥構造緩和時定数と、再結合過程における欠陥構造緩和時定数との間に強い正の相関関係があることを発見し、電子捕獲・再結合過程における可逆的な欠陥構造緩和過程の存在を発見した. Capture of Captu

本件では欠陥構造緩和についてさらに考 察する.図2に示すように構造緩和が Dlike 準位の伝導帯電子捕獲直後,および, A-like 準位捕獲電子の再結合直後に起きて いることから, 伝導帯電子の捕獲時の放出 エネルギー、および、A-like 準位捕獲電子 の再結合時の放出エネルギーが構造緩和の エネルギー源と推測される.しかし、例え ばタイプ1欠陥では、伝導帯電子のD-like 準位への捕獲過程は存在するためこの放出 エネルギーで構造緩和が生じ得るが、A-like 準位の捕獲電子は伝導帯に放出されていて 再結合過程に寄与しないため構造緩和が生 じ得ないことになる. これは CP サイクル の繰返しによる可逆的な構造緩和と矛盾す る. 図3に示すように電子捕獲・放出(再 結合に限らない)に伴い欠陥内の電荷バラ ンスに変化が生じ、系安定化のために可逆 的に構造緩和が生じると考える. 欠陥のタ イプによって検出できる遷移過程が異なる ことを考慮することですべての実験結果を 矛盾なく説明することが可能である.

Fig. 1 Classification of single amphoteric Si/SiO<sub>2</sub> interface-defects [1, 2].

Fig. 2 Electron capture/emission processes occurring at a Type-9 defect during one cycle of the gate pulse using the schematic energy-band diagrams.

Fig. 3 State transitions including lattice relaxation associated with the capture and emission of electrons during one cycle of the gate pulse.

本研究の一部は科研費 No. 20H02203 の助成を受けて行われた. 参考文献

- [1] T. Tsuchiya and Y. Ono, JJAP 54, 04DC01, 2015.

- [3] P. M. Lenahan et al., IEEE T-NS 48(6), p. 2131, Dec. 2001.

- [5] 土屋 他, 第 84 回秋応物 21a-A304-10~11, 2023.

- [7] 土屋 他, 第 70 回春応物 16a-A403-9~10, 2023.

- [2] T. Tsuchiya and P. M. Lenahan, JJAP 56, 031301, 2017.

- [4] 土屋 他, 第 69 回春応物 23p-E307-18~20, 2022.

- [6] 土屋 他, 第83 回秋応物 22a-A102-1~2, 2022.

- [8] 土屋 他, 第 71 回春応物 23a-12J-5~6, 2024.

# MOS 界面の単一欠陥チャージポンピングによって可能となった 両性準位における電子捕獲素過程の直接観測(13) -準位深さの影響-

Direct observation of electron capture processes in amphoteric defect states achieved by charge pumping in individual defects at MOS interface (13) -Effects of level depth-

静大電研 <sup>○</sup>土屋敏章,堀 匡寬,小野行徳

Shizuoka Univ., <sup>O</sup>Toshiaki Tsuchiya, Masahiro Hori, Yukinori Ono E-mail: tsuchiva.toshiaki@shizuoka.ac.jp

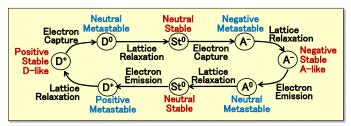

これまで我々はチャージポンピング(CP)法によってナノ MOS 素子内に存在する MOS 界面欠陥の 単一性の判定法を確立し、単一欠陥からの CP 電流  $I_{CPS}$  が  $0\sim 2fq$  (f:ゲートパルス周波数, q:電気素量) の様々な値を示すことを発見した[1]. これにより単一欠陥が 2 電子準位を有していることを実証し, すべての  $I_{CPS}$  値を説明できる単一欠陥の 10 種のタイプ分類を行った(図 1). また,  $I_{CPS} = fq$  一定を大前 提としている従来 CP 理論を本質的に改訂した[2]. さらに、単一界面欠陥の 2 電子準位の密度分布 (DOS) を導出し、既報[3]の ESR による  $P_{b0}$  センターの DOS との一致性を示した。そして、各準位に おける伝導帯電子の捕獲時定数の実測[4]、および、各準位に捕獲された電子の価電子帯ホールとの再 結合時定数の実測に成功し[5],これらの値の考察からこの2電子準位がドナー型(D-like)とアクセブ

タ型(A-like)の両性を有することに整合することを 実証した.以上の結果から,界面欠陥がPboセンター であることを単一欠陥単位(原子スケール)ではじめ て実証した.さらに,D-like および A-like 準位への連 続的な伝導帯電子捕獲素過程の観測から,D-like 準位 が電子捕獲した直後に欠陥構造緩和が起きていること の直接観測に成功した[6][7]. また, 両準位に捕獲され ている電子が価電子帯ホールと連続的に再結合する素 過程の観測から、A-like 準位の捕獲電子が再結合した 直後に欠陥構造緩和が起きていることの直接観測に成 功した[8]. さらに、電子捕獲過程における欠陥構造緩

和時定数と、再結合過程における欠陥構造緩和時定数の間に強 い正の相関関係を発見し,電子捕獲・再結合過程における可逆 的な欠陥構造緩和過程の存在を発見した.

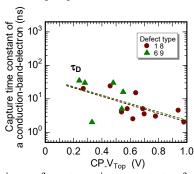

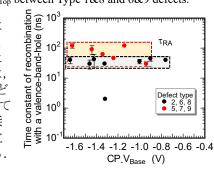

本件では単一欠陥の A-like や D-like 準位における電子捕獲・ 再結合時定数に及ぼす各準位深さの影響を検討する. τΑ (τρ)を A-like (D-like)準位への伝導帯電子の捕獲時定数, τ<sub>RA</sub>(τ<sub>RD</sub>)を Alike (D-like)準位に捕獲された電子の再結合時定数とする. τ<sub>A</sub> に ついては欠陥 Type2 と 5 の比較を行い、A-like 準位深さによる 有意差は無かった. τD については Type1,8 と Type6,9 の比較を 行った(図2). 図から、バラツキはあるが最小二乗法による両 者の回帰直線はほぼ同一であり, 準位深さの影響

は見られない. 従って, 両準位とも電子捕獲時定 数は準位深さに依存しておらず、少なくともバン ドギャップ中心 Ei±0.3 eV の範囲内では両準位の捕獲断面積は 各々一定と言える. なお, 図2の横軸 CP V<sub>Top</sub>は各単一欠陥位

置における伝導帯電子濃度を統一するために欠陥毎に設定した ゲートパルスの Top 電圧であり、 $\tau_D$ が CP  $V_{Top}$ に依存するのは、 D-like 準位の捕獲断面積が大きいため、 $CP_{-}V_{Top}$ が高い欠陥ほど 実効的な電子濃度が高くなるためである[7]. 一方, τ<sub>RA</sub>について は Type2,6,8 と Type5,7,9 の比較を行った(図3). 図から,深 い準位 (Type5, 7, 9) の方がτ<sub>RA</sub> は大きい傾向にある. 深い準位 ほど捕獲電子に対する原子核の束縛力が強いためと考えられる.

なお、τ<sub>RD</sub>についてはデータ不十分なため省略する. 本研究の一部は科研費 No. 20H02203 の助成を受 けて行われた.

#### 参考文献

- [1] T. Tsuchiya and Y. Ono, JJAP 54, 04DC01, 2015.

- [3] P. M. Lenahan et al., IEEE T-NS 48(6), p. 2131, Dec. 2001.

- [5] 土屋 他, 第 84 回秋応物 21a-A304-10~11, 2023.

- [7] 土屋 他, 第 70 回春応物 16a-A403-9~10, 2023.

Fig. 1 Classification of single amphoteric Si/SiO<sub>2</sub>

interface-defects [1, 2].

Fig. 2 Comparison of capture time constant of a conduction-band electron at a D-like state  $\tau_D$  dependence upon CP\_V<sub>Top</sub> between Type 1&8 and 6&9 defects.

Fig. 3 Comparison of recombination time constant of an electron captured at an electron captured at an A-like state with a valence-band-hole  $\tau_{RA}$  as a function of  $CP\_V_{Base}$  between Type 2, 6, 8 and Type 5, 7, 9 defects.

- [2] T. Tsuchiya and P. M. Lenahan, JJAP 56, 031301, 2017.

- [4] 土屋 他, 第 69 回春応物 23p-E307-18~20, 2022.

- [6] 土屋 他, 第83 回秋応物 22a-A102-1~2, 2022.

- [8] 土屋 他, 第 71 回春応物 23a-12J-5~6, 2024.

## 等電子トラップ TFET に内在する二重量子ドットの大規模特性評価

Large-scale Characterization of Double Quantum Dots in Isoelectronic-Trap-Assisted Tunnel Field-Effect Transistors 産総研 <sup>O</sup>(P) 千足 勇介,稲葉 工,八木下 淳史,加藤 真,石川 智弘,岡 博史,加藤 公彦,浅井 栄大,小倉 実,中山 隆史,飯塚 将太,森 貴洋

National Institute of Advanced Industrial Science and Technology (AIST)

\*Yusuke Chiashi, Takumi Inaba, Atsushi Yagishita, Makoto Kato, Tomohiro Ishikawa, Hiroshi Oka,

Kimihiko Kato, Hidehiro Asai, Minoru Ogura, Takashi Nakayama, Shota Iizuka, and Takahiro Mori

#### E-mail: yusuke.chiashi@aist.go.jp

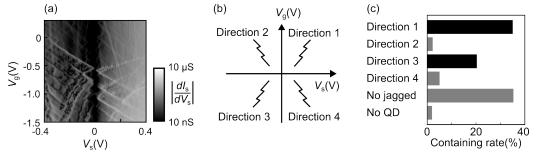

量子コンピュータやセンサをはじめとする量子技術の応用へ向けて、シリコンスピン量子ビットに注目が集まっている。我々はこれまで、等電子トラップ援用トンネルトランジスタ(IET-TFET)において、10 K までの高温量子ビット動作に成功してきた[1]。IET-TFET の量子ビット動作には、電子を閉じ込める量子ドットが直列に結合した二重量子ドット構造が利用される。一方の量子ドットは IET によるものだと考えられるが、もう一方は偶発的に存在した未知の量子ドットであり由来は明らかとなっていない。

今回、偶発的に存在した量子ドットの正体を探るべく、4K において 354 個の IET-TFET 素子を評価し、二重量子ドット特性の統計を評価した結果を報告する。実験では 300 mm 極低温オートプローバーを用いて、300 mm ウエハ上に形成した IET-TFET を評価した。

Fig. 1(a)は IET-TFET から観測された典型的な微分コンダクタンスの電圧マッピングである。量 子ドットを介した伝導により、様々な特徴線が生じている様子が確認される。特徴線のうち、左 下 V<sub>s</sub> < 0 V に観測されるギザギザ線は、二重量子ドットにおいて片方のドットに連続して電子が 入る様子を反映しており[2]、以前報告された量子ビットとして動作する素子においても観測され ている。ギザギザ線は二重量子ドットの捕獲可能電子数に差がある場合に生じることがわかって いる。一般に、IET のような単一不純物や欠陥が量子ドットとなる場合、捕獲可能な電子数は2 個となる。一方で不純物がクラスター化した場合には、その大きさに応じて捕獲可能電子数が増 加することが知られている[3]。よって観測されたギザギザ線は、IET 量子ドットと、クラスター 化した何らかの不純物もしくは欠陥のつくる量子ドットに由来することが示唆される。次に、統 計的傾向を探るため、取得した電圧マッピング全体について Fig. 1(b)のようにギザギザ線を方向 で分類した。Fig. 1(c)は電圧マッピングを分類したヒストグラムである。ギザギザ線は測定した全 デバイスのうち 63 %で観測され、出現するギザギザ線の方向が Direction 1 と 3 に偏っていること が明らかとなった。等価回路モデルを用いたシミュレーション[4]によってこれを解析すると、こ の特徴を与える二重量子ドットは弱結合であり、またソース側に IET 量子ドットが、ドレイン側 にクラスター由来と考えられる量子ドットが存在する構造になっていることがわかった。弱結合 状態は、量子ビットの動作に必要なスピンブロッケイド現象の発現条件でもあり、本素子が量子 ビット動作するという事実とも矛盾がない。更なる高温動作の実現には、クラスター由来量子ド ットを消失させ、別途制御された量子ドットを形成する必要がある。

【謝辞】本研究は文部科学省光・量子飛躍フラッグシッププログラム(Q-LEAP) JPMXS0118069228 の一環として実施された。本研究におけるデバイスは産総研スーパークリーンルーム(SCR)において試作された。【参考文献】 [1]K. Ono et.al., Sci. Rep. 9, 469 (2019). [2] T. Ota et.al., Phys. Rev. Lett. 93, 066801(2004). [3] D. Moraru et.al., Sci. Rep. 4, 6219 (2014). [4] A. V. Danilov et.al., Phys. Rev. B 65, 125312 (2002).

Figure 1 (a)The differential conductance of the source current. (b)The classification of jagged pattern. (c) The histogram of the jagged patterns on 354 TFETs. No QD means the samples without coulomb blockade feature.

# P型 Si 二重量子ドットにおける磁場に依存した 量子キャパシタンスの評価

Evaluation of magnetic field-dependent quantum capacitance

in a p-type Si double quantum dot

東工大<sup>1</sup>, 日立研開<sup>2</sup> °和田 陸久<sup>1</sup>, 溝口 来成<sup>1</sup>, 近藤 知宏<sup>1</sup>, 土屋 龍太<sup>2</sup>, 峰 利之<sup>2</sup>, 久本 大<sup>2</sup>, 水野 弘之<sup>2</sup>, 米田 淳<sup>1</sup>, 小寺 哲夫<sup>1</sup>

Tokyo Tech <sup>1</sup>, R&D Group, Hitachi Ltd. <sup>2</sup>, <sup>o</sup>Riku Wada<sup>1</sup>, Raisei Mizokuchi<sup>1</sup>, Chihiro Kondo<sup>1</sup>, Ryuta Tsuchiya<sup>2</sup>, Toshiyuki Mine<sup>2</sup>, Digh Hisamoto<sup>2</sup>, Hiroyuki Mizuno<sup>2</sup>, Jun Yoneda<sup>1</sup>, Tetsuo Kodera<sup>1</sup> E-mail: wada.r.ad@m.titech.ac.jp

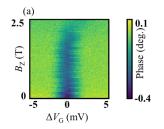

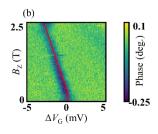

シリコンスピン量子ビットのスピン状態読出しにおいて重要な役割を果たすパウリスピン閉塞 (PSB)という現象では、様々な要因が PSB を解除し、読み出しの妨げになるといった問題がある。 PSB を解除する要因の一つに、スピン軌道相互作用(SOC)がある[1]。SOC はp型のデバイスで強 く働き、集積化に適した高速なスピン操作に利用されてきた。本研究では、PSB における SOC の 影響の理解に向け、p型シリコン二重量子ドットのドット間電荷遷移(ICT)の磁場依存性を調べた。 実験では、ゲートセンシングという手法を用いて[2]、いくつかの ICT における量子キャパシタ ンスの磁場依存性を調べた(Fig.1)。ゲートセンシングでは、ゲート電極に高周波を印加し、その反 射波の位相変化からキャパシタンス変化を読み取る。ドット間のトンネル結合が十分に大きく、 遷移が可能なスピン状態間のトンネリングであれば量子キャパシタンスが生じる。今回の結果で は、それぞれの ICT で異なる磁場依存性が見えていることから、各 ICT でのスピン状態や SOC の 大きさが異なっていることが示唆される。Fig. 1(a)では、磁場によって、量子キャパシタンスを持 つ準位から持たない準位へ基底準位の遷移が現れており、典型的な PSB が生じていると考えられ る。一方で、Fig. 1(b)の ICT では、0.3 T以上では磁場に比例して ICT の位置が変わっている。こ のような振る舞いは、異なる磁場依存性をもつ準位間が強い SOC 等によって結合することで量子 キャパシタンスが生じている場合に観測される。講演では、上記の結果をより詳細に解析し、PSB 解除に対する SOC の影響について議論する予定である。

本研究は JST Moonshot R&D Grant Number JPMJMS2065, MEXT Quantum Leap Flagship Program (MEXT QLEAP) Grant No. JPMXS0118069228, JST さきがけ(JPMJPR21BA), 科研費(JP23H05455, JP23H01790, JP23K17327)の支援を受けて遂行された。

[1] T. Lundberg, et al., npj Quantum Inf. 10, 28 (2024). [2] J.I. Colless, et al., Phys. Rev. Lett. 110, 046805 (2013).

Fig.1 Magnetic field dependences of ICTs.

#### シリコンPN単電荷ポンプによる電子正孔比較

#### Comparison of electron and hole by a silicon PN single-charge pump

NTT 物性基礎研 ○山端 元音、藤原 聡

# NTT Basic Research Labs., <sup>O</sup>Gento Yamahata and Akira Fujiwara

E-mail: gento.yamahata@ntt.com

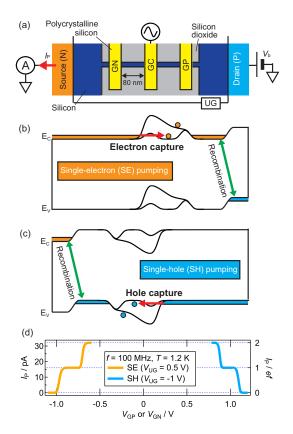

クロック制御により電荷を一つずつ転送する単電荷ポンプは正確な電流生成が可能であるため電流標準への応用が期待される[1]。応用へ向け、歩留まり良く高精度動作が可能な素子設計条件を見出す必要がある[2]。一つの指針として、有効質量の重い正孔を使うことにより転送精度向上が期待され、これまで極低温での特性評価により単正孔ポンプの優れた特性を観測してきた[3,4]。一方、より正確にデバイス物理を理解するためには単一の素子での電子と正孔の比較が望ましい。今回、P型とN型の電極を持つ単電荷ポンプを利用し電子と正孔の特性を比較したので報告する。

素子の概略図を図1(a)に示す。直径10 nm オー ダーのシリコン細線上に3つの微細ゲート電極(GN, GC, GP)を持つ。細線及び細線と繋がる幅広部分は もう1層のゲート電極 (UG) に覆われている。UG の外側領域をそれぞれ N型(リン)、P型(ボロン) に不純物ドープし、N型ソース、P型ドレインを形 成した。動作原理を図1(b)、(c)のポテンシャル図 で説明する。まず、ドレイン側(b)もしくはソース 側(c)での再結合電流を十分大きくするためドレイ ン側にバイアス電圧 V<sub>b</sub> ~ 1 V を印加した。UG の 電圧により細線領域に存在する電荷を選択できる。 単電荷転送では入口障壁の形状が重要となるため [4]、今回は GC に高周波電圧 (周波数 f) を印加し どちらの極性でも入口障壁となるようにして電子 正孔比較を行った。この際、単電子(単正孔)の 場合は GP(GN)に負(正)の DC 電圧を印加し出 口側障壁を形成した。これにより単電子もしくは 単正孔を転送し正確な電流 Ip = ef (e:電荷素量) を得ることができる。図 1(d) に電流電圧特性の一 例を示す。単電子転送と単正孔転送を単一の素子 で観測することに成功した。更に、温度依存性と 周波数依存性を調べた結果、数百 MHz 程度までは 正孔が優位な特性を持つことが分かった。単一の 素子を利用した電子と正孔の初めての比較であり、 今後の素子設計における重要な知見である。

参考文献: [1] G. Yamahata *et al.*, Appl. Phys. Lett. **109**, 013101 (2016). [2] A. Fujiwara *et al.*, ECS Trans. **112**, 119 (2023). [3] G. Yamahata *et al.*, Appl.

Fig. 1: (a) Schematic of the device with a part of the electrical connections. (b, c) Schematic potential diagrams for single-electron (SE) and single-hole (SH) pumping. (d)  $I_P$  and  $I_P/ef$  as a function of  $V_{GP}$  (SE pumping) or  $V_{GN}$  (SH pumping).

Phys. Lett. 106, 023112 (2015). [4] G. Yamahata et al., J. Appl. Phys. 135, 014502 (2024).