Oral presentation | 17 Nanocarbon and Two-Dimensional Materials : 17.3 Layered materials

## [20p-A31-1~14] 17.3 Layered materials

Mahito Yamamoto(Kansai University)

1:15 PM - 1:30 PM JST | 4:15 AM - 4:30 AM UTC

[20p-A31-1]

Fabrication of suspended 2D materials using plasticized polyvinyl chloride

OMomoko Onodera<sup>1</sup>, Manabu Ataka<sup>1</sup>, Yijin Zhang<sup>1</sup>, Rai Moriya<sup>1</sup>, Kenji Watanabe<sup>2</sup>, Takashi Taniguchi<sup>2</sup>, Hiroshi Toshiyoshi<sup>1</sup>, Tomoki Machida<sup>1</sup> (1.IIS, Univ. of Tokyo, 2.NIMS)

1:30 PM - 1:45 PM JST | 4:30 AM - 4:45 AM UTC

[20p-A31-2]

Assessing point defects in CVD-grown monolayer WSe<sub>2</sub> using conductive AFM

O(M1)Yuta Sawai<sup>1</sup>, Takahiko Endo<sup>1</sup>, Yasumitsu Miyata<sup>1</sup> (1.Tokyo Metro. Univ.)

1:45 PM - 2:00 PM JST | 4:45 AM - 5:00 AM UTC

[20p-A31-3]

Photoluminescence properties of monolayer MoSe<sub>2</sub> grown on mica substrate

OTakahiko Endo<sup>1</sup>, Wenjin Zhang<sup>1</sup>, Kenji Watanabe<sup>2</sup>, Takashi Taniguchi<sup>2</sup>, Yasumitsu Miyata<sup>1</sup> (1.Tokyo Metro. Univ., 2.NIMS)

2:00 PM - 2:15 PM JST | 5:00 AM - 5:15 AM UTC

[20p-A31-4]

Photoluminescence properties of Janus WSSe/WSe<sub>2</sub> heterobilayers on hBN substrate

OTomoya Ogawa<sup>1</sup>, Wenjin Zhang<sup>1</sup>, Hiroshi Nakajo<sup>2,3,4</sup>, Soma Aoki<sup>2,3</sup>, Yuto Urano<sup>5</sup>, Takahiko Endo<sup>1</sup>, Yusuke Nakanishi<sup>1</sup>, Kenji Watanabe<sup>5</sup>, Takashi Taniguchi<sup>5</sup>, Toshiaki Kato<sup>2,3</sup>, Ryo Kitaura<sup>5</sup>, Yasumitsu Miyata<sup>1</sup> (1.Tokyo Metro. Univ., 2.Tohoku Univ., 3.AIMR Tohoku Univ., 4.KOKUSAI ELECTRIC CORP., 5.NIMS)

2:15 PM - 2:30 PM JST | 5:15 AM - 5:30 AM UTC

[20p-A31-5]

Carrier Modulation of Monolayer MoS<sub>2</sub> by Remote Ferroelectric Doping and the Screening Effect Induced by h-BN Spacer Layers

OKAIPENG RONG<sup>1</sup>, Ryosuke Noro<sup>2</sup>, Hayato Nishigaki<sup>2</sup>, Mingda Ding<sup>2</sup>, Yao Yao<sup>2</sup>, Taiki Inoue<sup>2</sup>, Ryuji Katayama<sup>2</sup>, Yoshihiro Kobayashi<sup>2</sup>, Kazunari Matsuda<sup>3</sup>, Shinichiro Mouri<sup>1</sup> (1.Ritsumeikan Univ., 2.Osaka Univ., 3.Kyoto Univ.)

2:30 PM - 2:45 PM JST | 5:30 AM - 5:45 AM UTC

[20p-A31-6]

PVD-MoS<sub>2</sub> film with SVA through in-situ-ALD-Al<sub>2</sub>O<sub>3</sub> film

OShunsuke Nozawa<sup>1</sup>, Shungo Okamura<sup>1</sup>, Naoki Matsunaga<sup>1</sup>, Keita Kurohara<sup>1</sup>, Hitoshi Wakabayashi<sup>1</sup> (1.Tokyo Tech)

2:45 PM - 3:00 PM JST | 5:45 AM - 6:00 AM UTC

[20p-A31-7]

Evaluation of F6-TCNNQ monolayer deposition on WSe<sub>2</sub>

OKensho Matsuda<sup>1</sup>, Takuya Kojima<sup>1</sup>, Yuto Noguchi<sup>1</sup>, Mengnan Ke<sup>1</sup>, Shohei Kumagai<sup>2</sup>, Toshihiro Okamoto<sup>2</sup>, Nobuyuki Aoki<sup>1</sup> (1.Chiba Univ., 2.Tokyo Tech Univ.)

3:15 PM - 3:30 PM |ST | 6:15 AM - 6:30 AM UTC

[20p-A31-8]

The analytical method for evaluation of interface state density of 2D semiconductor channel materials

O(M1)Masaru Sato<sup>1</sup>, Ryu Hasunuma<sup>1</sup> (1.Univ. of Tsukuba)

3:30 PM - 3:45 PM JST | 6:30 AM - 6:45 AM UTC

[20p-A31-9]

Thickness control of layered germanium arsenide film via thermal oxidation

OAyuta Hasumi<sup>1,2</sup>, Noriyuki Urakami<sup>1,2</sup>, Yoshio Hashimoto<sup>1,2</sup> (1.Shinshu Univ., 2.Shinshu Univ. RISM)

3:45 PM - 4:00 PM JST | 6:45 AM - 7:00 AM UTC

[20p-A31-10]

NbS<sub>2</sub> as a TMDC metal with a high effective work function

OKoki Hori<sup>1,2</sup>, Wen-Hsin Chang<sup>1</sup>, Toshifumi Irisawa<sup>1</sup>, Atsushi Ogura<sup>2,3</sup>, Naoya Okada<sup>1</sup> (1.AIST, 2.Meiji Univ., 3.MREL)

4:00 PM - 4:15 PM JST | 7:00 AM - 7:15 AM UTC

[20p-A31-11]

TMDC crystallinity on substrate temperature in in-situ-ALD-Al<sub>2</sub>O<sub>3</sub> cover formation

OTaiga Fuse<sup>1</sup>, Naoki Matsunaga<sup>1</sup>, Shungo Okamura<sup>1</sup>, Keita Kurohara<sup>1</sup>, Soma Ito<sup>1</sup>, Shunsuke Nozawa<sup>1</sup>, Takanori Shirokura<sup>1</sup>, Hitoshi Wakabayashi<sup>1</sup> (1.Tokyo Tech.)

4:15 PM - 4:30 PM JST | 7:15 AM - 7:30 AM UTC

[20p-A31-12]

Energetics and electronic structures of corrugated in-plane heterostructures of Janus WSSe

OMina Maruyama<sup>1</sup>, Susumu Okada<sup>1</sup>, Yanlin Gao<sup>1</sup> (1.Univ. Tsukuba)

4:30 PM - 4:45 PM JST | 7:30 AM - 7:45 AM UTC

[20p-A31-13]

Dependence of contact electrode shape on Ti/h-BN/CVD-monolayer MoS<sub>2</sub> interface

ODaiki Tsuruoka<sup>1</sup>, Takahiko Endo<sup>2</sup>, Yasumitsu Miyata<sup>2</sup>, Nobuyuki Aoki<sup>1</sup>, Mengnang Ke<sup>1</sup> (1.Chiba univ., 2.Tokyo Metropolitan Univ.)

4:45 PM - 5:00 PM JST | 7:45 AM - 8:00 AM UTC

[20p-A31-14]

Synthesis and performance evaluation of WTe<sub>2</sub> nanowires for thermoelectric applications

O(M1C)Wataru Ise<sup>1</sup>, Seiya Yokokura<sup>1,2</sup>, Hiroki Waizumi<sup>1,2</sup>, Toshihiro Shimada<sup>1,2</sup> (1.CSE. Hokkaido Univ., 2.Eng. Hokkaido Univ.)

## 軟質ポリ塩化ビニルを用いたサスペンド原子層構造作製法

Fabrication of suspended 2D materials using plasticized polyvinyl chloride 東京大学生産技術研究所 <sup>1</sup>. 物質·材料研究機構 <sup>2</sup>

O小野寺桃子<sup>1</sup>,安宅 学<sup>1</sup>,張奕勁<sup>1</sup>,守谷頼<sup>1</sup>,渡邊賢司<sup>2</sup>,谷口尚<sup>2</sup>,年吉洋<sup>1</sup>,町田友樹<sup>1</sup>

Institute of Industrial Science, University of Tokyo<sup>1</sup>, NIMS<sup>2</sup>

°Momoko Onodera, Manabu Ataka, Yijin Zhang, Rai Moriya, Kenji Watanabe, Takashi Taniguchi, Hiroshi Toshiyoshi, and Tomoki Machida

E-mail: monodera@iis.u-tokyo.ac.jp

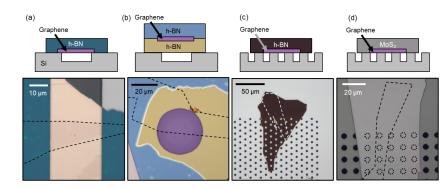

二次元層状物質を平坦な基板上から凹凸形状をもつ基板上へと転写することでサスペンド状態の原子層構造を作製できる。サスペンド構造は原子層の光学特性や力学特性を研究する上で非常に重要であり、高品質な劈開原子層を用いてサスペンド構造を作製する技術の開発が望まれる。本発表では、軟質ポリ塩化ビニル(PVC)膜を用いて SiO<sub>2</sub>/Si 基板上劈開原子層を任意の凹凸基板上に転写する方法を紹介する。軟質 PVC を用いると高温で PVC を溶かさずに原子層のみを基板に落とすことができる(ドライリリース)。よって転写後に溶剤に浸漬する必要がなく、原子層が破壊されるのを防ぐことができる。また、サスペンド構造作製に特化した PVC 膜の配合を工夫し、高確率で凹凸基板上への転写を可能とした。

Fig. 1: Photographs and schematics of suspended van der Waals heterostructures.

Fig. 2: Suspended h-BN/TLG device fabricated by this method.

[1] Momoko Onodera, Manabu Ataka, Yijin Zhang, Rai Moriya, Kenji Watanabe, Takashi Taniguchi, Hiroshi Toshiyoshi, and Tomoki Machida. under review

## 導電性 AFM を利用した CVD 成長単層 WSe2 の点欠陥評価

Assessing point defects in CVD-grown monolayer WSe<sub>2</sub> using conductive AFM 都立大理<sup>1</sup>, <sup>○</sup>澤井 悠太<sup>1</sup>, 遠藤 尚彦<sup>1</sup>,宮田 耕充<sup>1</sup>

Tokyo Metro. Univ<sup>1</sup>., °Yuta sawai<sup>1</sup>, Takahiko Endo<sup>1</sup>, Yasumitsu Miyata<sup>1</sup> E-mail: sawai-yuta@ed.tmu.ac.jp

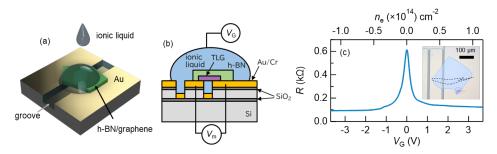

遷移金属ダイカルコゲナイド(TMD)は、その二次元構造と優れた電子輸送特性により、次世代の半導体材料として注目を集めている。その物性の理解と応用に向け、欠陥密度の定量と制御は重要な課題となっている。一般に、TMDには、カルコゲン空孔や金属不純物などを含む多数の点欠陥が存在し(図 1a)、それらはドーパント、キャリア散乱、非輻射励起子再結合、電子構造の不均一性の要因となる[1,2]。近年、点欠陥の簡便な評価法として、導電性原子間力顕微鏡(C-AFM)を利用した研究が報告されてきた[2-4]。しかし、試料の高結晶試料の合成に向けた指針は未だ研究段階である。本研究では、CVDで成長した単層 WSe2を対象に、C-AFMを利用した点欠陥の評価に取り組んだ。

単層 WSe<sub>2</sub>は、CVD 法によってグラファイト上に直接合成した[5]。グラファイトと導電性短針の間に電圧を印加し、C-AFM 測定を行った(図 1a)。図 1b に単層 WSe<sub>2</sub>の電流像の例を示す。この試料では、電流が増大する点(白点)が約  $8\times10^9$  個/cm² の密度で存在することが観測された。この密度は先行研究で観測された CVD 成長単層 WS<sub>2</sub>の低欠陥領域と比べて半分程度となる[2]。電流値の増加は金属不純物のギャップ内準位を介した共鳴アシストトンネルで解析されており[4]、本試料における電流増加点は合成中に混入した金属不純物であることが示唆される。また、合成条件に依存し、この欠陥密度が  $3\times10^{10}$  個/cm² 以上に変化することが確認された(図 1c)。これらの結果は、点欠陥の制御や物性との相関関係の解明に向けた重要な知見になると期待される。

Figure 1. (a) Schematic of conductive AFM of monolayer WSe<sub>2</sub> containing impurity metal atoms (red, blue) as point defects. (b,c) Current images of monolayer WSe<sub>2</sub> grown on graphite with different growth conditions.

[1] W. Zhou et al., Nano Left. 13, 2615-2622 (2013)., [2] R. Rosenberger et al., ACS Nano 12, 1793-1800 (2018)., [3] K. Xu et al., ACS Nano 17, 24743-24752 (2023)., [4] T. Vu et al., ACS Nano 17, 15648-15655 (2023)., [5] Y. Kobayashi et al., ACS Nano 9, 4056-4063 (2015).

## マイカ基板上に成長した単層 MoSe<sub>2</sub>の発光特性

Photoluminescence properties of monolayer MoSe<sub>2</sub> grown on mica substrate 都立大理 <sup>1</sup>, 物材機構 <sup>2</sup> <sup>0</sup>遠藤 尚彦 <sup>1</sup>, 張 文金 <sup>1</sup>, 渡邊 賢司 <sup>2</sup>, 谷口 尚 <sup>2</sup>, 宮田 耕充 <sup>1</sup>

Tokyo Metropolitan Univ. <sup>1</sup>, NIMS <sup>2</sup>, OTakahiko Endo <sup>1</sup>, Wenjin Zhang <sup>1</sup>,

Kenji Watanabe<sup>2</sup>, Takashi Taniguchi<sup>2</sup>, Yasumitsu Miyata<sup>1</sup>

E-mail: t.endo.phys.se.tmu@outlook.jp

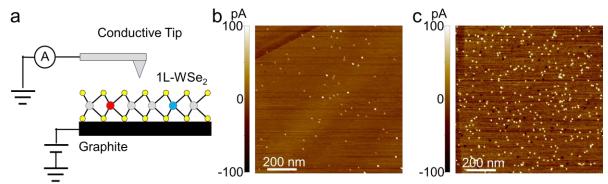

遷移金属ダイカルコゲナイド(TMD)は、その二次元構造と優れた半導体特性より、次世代の電子デバイスへの応用が期待されている。その本来の特性を活用するために、TMDと基板の相互作用の理解は重要な課題である。特に、シリコン酸化膜上などでは、格子歪みやドーピングにより TMD、電子構造、発光特性、ギャップ内準位などに不均一性が現れる。また、このような不均一性はグラファイトや六方晶窒化ホウ素(hBN)などの平坦な基板上では抑制されていることが報告されている[1]。グラファイトや hBN と同様の層状物質として、マイカ(雲母)単結晶基板がしばしば TMD の成長に利用されており[2,3]、マイカ基板と TMD の相互作用は興味深い。しかしながら、マイカ上に成長した TMD の発光特性についてはほとんど知られていなかった。本研究では、マイカ単結晶上に成長した単層 MoSe2 の発光特性を調べた。

単層 MoSe<sub>2</sub> は化学気相成長法を用いて、マイカ、シリコン、hBN 基板上に合成した。Figure 1 は、各基板上の単層 MoSe<sub>2</sub> 単結晶の異なる箇所から取得した発光のピークエネルギーと半値幅の

関係を示す。ピーク値に関しては、マイカ上試料は約1.56 eV とhBN 上の値と近く、シリコン上の値と比べてピーク値の分布も小さい。この結果は、マイカ基板では、hBN と同様に表面の平坦性より成長後の冷却時に熱歪みが導入されにくいことを示唆している。一方、半値幅はマイカ上試料では40~70 meV の間に広く分布した。この半値幅の不均一性の起源としては、マイカ上の荷電不純物やMoSe2の欠陥などが挙げられる。これらの結果は、マイカ上での結晶成長、および高品質 TMD の合成に向けた重要な指針になると期待される。

- [1] Y. Kobayashi, et al., ACS Nano 9, 4056 (2015)

- [2] J. Xia, et al., Nanoscale 6, 8949 (2014)

- [3] M. Okada, et al., ACS Nano 16, 13069 (2022)

Figure 1. (a) PL peak energy vs. FWHM map of monolayer  $MoSe_2$  grown on mica,  $SiO_2$  and hBN substrates.

## hBN 基板上ヤヌス WSSe/WSe2 ヘテロ二層の発光特性

Photoluminescence properties of Janus WSSe/WSe<sub>2</sub> heterobilayers on hBN substrate 都立大理 <sup>1</sup>, 東北大工 <sup>2</sup>, 東北大 AIMR<sup>3</sup>, KOKUSAI ELECTRIC(株)<sup>4</sup>, 物材機構 <sup>5</sup>

O(M2)小川 朋也<sup>1</sup>, 張 文金<sup>1</sup>, 中條 博史<sup>2,3,4</sup>, 青木 颯馬<sup>2,3</sup>, 浦野 裕斗<sup>5</sup>, 遠藤 尚彦<sup>1</sup>, 中西 勇介<sup>1</sup>, 渡邊 賢司<sup>5</sup>, 谷口 尚<sup>5</sup>, 加藤 俊顕<sup>2,3</sup>, 北浦 良<sup>5</sup>, 宮田 耕充<sup>1</sup>

Tokyo Metro. Univ.<sup>1</sup>, Tohoku Univ.<sup>2</sup>, AIMR Tohoku Univ.<sup>3</sup>, KOKUSAI ELECTRIC CORP.<sup>4</sup>, NIMS<sup>5</sup>

T. Ogawa<sup>1</sup>, W. Zhang<sup>1</sup>, H. Nakajo<sup>2,3,4</sup>, S. Aoki<sup>2,3</sup>, Y. Urano<sup>5</sup>, T. Endo<sup>1</sup>,

Y. Nakanishi<sup>1</sup>, K. Watanabe<sup>5</sup>, T. Taniguchi<sup>5</sup>, T. Kato<sup>2,3</sup>, R. Kitaura<sup>5</sup>, and Y. Miyata<sup>1</sup> E-mail: ogawa-tomoya@ed.tmu.ac.jp

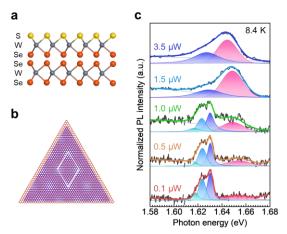

TMD モアレ超格子は、周期ポテンシャルに由来する強相関物理や量子光学現象より、近年注目を集めている。一般に、モアレ超格子は転写や気相成長により作製されるが、ごく最近、我々のグループではカルコゲン原子置換を利用したモアレ超格子の作製に成功した[1]。この手法では、例えば二層 WSe2の最表面のセレン原子を硫黄原子に置換することで、ヤヌス WSSe/WSe2へテロニ層を形成する(Figure 1a, b)。ここで、ヤヌス WSSe と WSe2の格子不整合より、このヘテロニ層はモアレ超格子となる。しかしながら、先行研究では、発光の広い線幅やスペクトルの不均一性より、その本来の光学応答が不明瞭な点が課題であった[1]。主な理由として、SiO2/Si 基板上での原子置換より生じた不均一な格子歪みが挙げられる。この課題を解決するため、本研究では、六方晶室化ホウ素(hBN)を基板として用い、格子歪みを抑制した光学的に高品質なヤヌス WSSe/WSe2 二層の合成と評価を行った。

Figure 1c に 8.4 K におけるヤヌス WSSe/WSe<sub>2</sub>の発光スペクトルの励起パワー依存性を示す。低励起パワーでは、1.63 eV 付近にピークを示し、6 meV程の間隔を持つ3つのピークでフィットできた。励起パワーが増加すると、各ピークはブロード化し、同時に1.65 eV 付近に新たなピークが出現した。これらのピークは、WSe<sub>2</sub>およびヤヌス WSSe では観測されず、モアレポテンシャルの影響を受けた層間励起子の発光であることが示唆される。発表では、原子置換における基板の効果や、発光ピークの起源について議論する。

Figure 1. Structural model of (a) the Janus WSSe/WSe<sub>2</sub> heterobilayer and (b) the moiré superlattice. (c) Photoluminescence (PL) spectra of the Janus WSSe/WSe<sub>2</sub> heterobilayer fabricated on hBN at 8.4 K.

## 強誘電リモートドーピングによる単層 MoS₂のキャリア変調 および h-BN 中間層による遮蔽効果

Carrier Modulation of Monolayer MoS<sub>2</sub> by Remote Ferroelectric Doping and

the Screening Effect Induced by h-BN Spacer Layers

立命館大理工<sup>1</sup>, 阪大工<sup>2</sup>, 京大工ネ研<sup>3</sup> <sup>○</sup>栄 凱蓬<sup>1</sup>, 野呂 諒介<sup>2</sup>, 西垣 颯人<sup>2</sup>, 丁 明达<sup>2</sup>, 姚 瑶<sup>2</sup>, 井ノ上 泰輝<sup>2</sup>, 片山 竜二<sup>2</sup>, 小林 慶裕<sup>2</sup>, 松田 一成<sup>3</sup>, 毛利 真一郎<sup>1</sup>

Ritsumeikan Univ.<sup>1</sup>, Osaka Univ.<sup>2</sup>, Kyoto Univ.<sup>3</sup>,

°Kaipeng Rong<sup>1</sup>, Ryosuke Noro<sup>2</sup>, Hayato Nishigaki<sup>2</sup>, Mingda Ding<sup>2</sup>, Yao Yao<sup>2</sup>, Taiki Inoue<sup>2</sup>, Ryuji Katayama<sup>2</sup>, Yoshihiro Kobayashi<sup>2</sup>, Kazunari Matsuda<sup>3</sup>, Shinichiro Mouri<sup>1</sup>

E-mail: gr0466er@ed.ritsumei.ac.jp

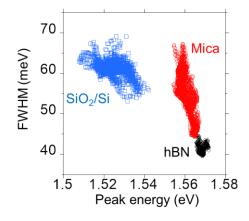

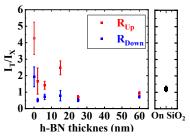

MoS<sub>2</sub>は代表的な遷移金属ダイカルコゲナイド(TMDs)材料として、次世代光・電子デバイスへの応用が期待されている。TMDs デバイス開発におけるキャリア変調手法について、Nb 原子ドーパント[1]、化学ドーピング[2]、および強誘電ゲーティング[3]など、様々な方法が提案された。本研究では、異なる厚さの h-BN 中間層を使用し、強誘電基板によるリモートドーピング法を提案する。我々の研究は、強誘電ドーピング手法を発展させ、基板の分極方向を制御することと h-BN 中間層を導入することによって単層 MoS<sub>2</sub>キャリア密度をリモートで空間変調させる可能性を示し、h-BN 厚みの変化による効果を調べた。

本研究では、我々は機械的剥離した 1L-MoS<sub>2</sub>/h-BN を周期的に分極反転された MgO:LiNbO<sub>3</sub> 基板上に転写した。 サンプルの概略図は Figure 1 のように示される。次に、1L-MoS<sub>2</sub> のキャリア密度を調べるために、フォトルミネッ

ドメイン( $R_{Down}$ )上の  $MoS_2$  のトリオン発光( $I_T$ ,  $\sim$ 1.84 eV)と励起子発光( $I_X$ ,  $\sim$ 1.88 eV)の PL 強度比と、h-BN 中間層の厚みとの依存性を示した。 Mass action law によると、 $I_T$  と  $I_X$  の比率はキャリア密度に比例することが知られている。従って、この結果は h-BN 厚みが 20 nm 未満のときに基板分極による顕著なリモートドーピング効果がみられ、h-BN の厚みが増すにつれてその効果が弱くなることを示唆している。また、距離に対する減衰特性は、h-BN の誘電遮蔽特性を考慮した 3D Thomas-Fermiモデル[4]を用いた計算で再現できる。本手法でのリモートドーピング効果は、h-BN中間層が 10 nm 以上の厚みでも保持されており、以前に報告された薄い h-BN 中間

層を介したトンネル電荷移動によるリモートドーピング[5]とは異なるメカニズムで

Figure 1 Schematic image of samples

Figure 2  $I_T/I_X$  plots corresponding to

different h-BN thickness

## 【参考文献】

- [1] B. Radisavljevic et al., Nat. Mater. 12, 815–820 (2013). [3] L. Lv et al., Nat. Commun. 10, 3331 (2019).

- [2] S. Mouri et al., Nano Lett. 13 (12), 5944-5948 (2013). [4] L. Li et al., Nano Lett. 12(1), 218-223 (2015).

- [5] J. Jang et al., Sci. Adv. 8, eabn3181(2022).

起こされる新たなリモートドーピング手法と考えられる。

## 【謝辞】

This work was supported by JSPS KAKENHI grant number 22H05471, 21H01017, 21K18913, and NEDO Intensive Support Program for Young Promising Researchers".

## In-situ-ALD-Al<sub>2</sub>O<sub>3</sub>越しに SVA を施した PVD-MoS<sub>2</sub>膜

## PVD-MoS<sub>2</sub> film with SVA through in-situ-ALD-Al<sub>2</sub>O<sub>3</sub> film

## 東工大, 〇野澤 俊輔, 岡村 俊吾, 松永 尚樹, 黒原 啓太, 若林 整

Tokyo Institute of Technology, °Shunsuke Nozawa, Shungo Okamura, Naoki Matsunaga,

## Keita Kurohara and Hitoshi Wakabayashi, E-mail: nozawa.s.ac@m.titech.ac.jp

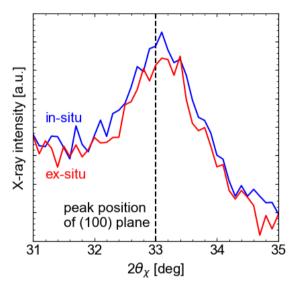

【緒言】トランジスタの微細化が進むにつれてシリコンの移動度は低下するため、次世代FET の新たなチャネル材料として  $MoS_2$  膜が注目されている $^{[1]}$ 。 FET の作製ではその上に High-k 膜を堆積する必要がある $^{[2]}$ が、 $MoS_2$  膜を堆積後に ex-situ で  $Al_2O_3$  を堆積すると、 $MoS_2$  膜の表面が酸化されて膜質が劣化する 懸念がある $^{[3]}$ 。そこで本研究では  $MoS_2$  膜を スパッタ法により堆積した後、in-situ で  $Al_2O_3$  膜を ALD 法により成膜した試料と ex-situ により同様に成膜した  $MoS_2$  膜の結晶性の比較をし、in-situ の有効性を調査した。

【方法】スパッタ法により SiO<sub>2</sub> (700 nm)/n-Si 基板上に 1.3 nm の MoS<sub>2</sub> 膜を成膜した。その後 *in-situ* で ALD 法により Al<sub>2</sub>O<sub>3</sub> 膜(3 nm)を堆積した。Al<sub>2</sub>O<sub>3</sub> 膜の上から硫黄雰囲気中アニール(Sulfur Vapor Anneal)ができることが明らかとなっているため<sup>[3]</sup>、40 分間 700℃で SVAを行った。また同様に、MoS<sub>2</sub> 成膜後に Al<sub>2</sub>O<sub>3</sub> 膜の堆積を行うまでに 1 時間大気下に晒した。試料の評価は in-plane X-ray diffraction (XRD) により行った。

【結果】Figure 1 に  $MoS_2$  膜の in-plane XRD に より測定した(100)面のピークを示す。また、このデータから Scherrer の式を用いて求めた  $^{[4]}$ グレインサイズを Table 1 に示す。in-situ の 方が ex-situ よりも半値幅が小さく、グレイン サイズが大きい事がわかった。つまり、 $MoS_2$  膜の膜質が高くなったと言える。

【結言】 $MoS_2$ 膜のスパッタ後に in-situ で ALD 法により High-k 膜を成膜するほうが ex-situ よりも  $MoS_2$  の膜質が高いことが明らかとなった。今回のプロセスでより結晶性の高い膜を用いた FET の作製を行う予定である。

【謝辞】本研究の一部は、文部科学省次世代 X-nics 半導体創生拠点形成事業(JPS011438), 及び JSPS 科研費(20H05880)の助成を受けた ものである。

Figure 1: In-plane XRD patterns around (100) plane of 1.3-nm MoS<sub>2</sub> films after deposition of Al<sub>2</sub>O<sub>3</sub> film and SVA.

Table 1: Peak position, FWHM and grain size determined from in-plane XRD patterns.

|         | $2\theta_{\chi}$ peak | FWHM  | Grain size |

|---------|-----------------------|-------|------------|

|         | [deg]                 | [deg] | [nm]       |

| in-situ | 33.0                  | 1.32  | 6.2        |

| ex-situ | 33.0                  | 1.43  | 5.7        |

#### 【参考文献】

- [1] Kentaro Matsuura, et al., Jpn. J. Appl. Phys., **59**, 080906 (2020).

- [2] Haruki Tanigawa, et al., Jpn. J. Appl. Phys., 59, SMMC01 (2020).

- [3] Masaya Hamada, et al., Jpn. J. Appl. Phys., **59**, 105501 (2020).

- [4] Shinya Imai, et al., EDTM, pp.316-318 (2023).

## WSe<sub>2</sub>上における F6-TCNNQ 単分子層形成評価

Evaluation of F6-TCNNQ monolayer deposition on WSe2

千葉大院<sup>1</sup>,東工大院<sup>2</sup>, <sup>0</sup>松田 健生<sup>1</sup>,小島 拓也<sup>1</sup>,野口 裕士<sup>1</sup>, 柯 梦南<sup>1</sup>, 熊谷 翔平<sup>2</sup>, 岡本 敏宏<sup>2</sup>, 青木 伸之<sup>1</sup>

ChibaUniv.<sup>1</sup>, TokyoTech<sup>2</sup>, <sup>O</sup>Kensho Matsuda<sup>1</sup>, Takuya Kojima<sup>1</sup>, Yuto Noguchi<sup>1</sup>, Mengnan Ke<sup>1</sup>, Shohei Kumagai<sup>2</sup>, Toshihiro Okamoto<sup>2</sup>, Nobuyuki Aoki<sup>1</sup> E-mail: n-aoki@faculty.chiba-u.jp

#### 1. はじめに

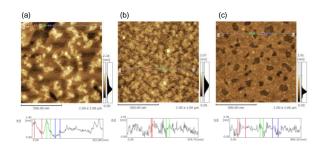

遷移金属ダイカルコゲナイド(TMDC)は二 次元層状物質であり、バンドギャップを持つ 半導体である. 層状物質であるため短チャネル効果に強く三次元半導体では実現困難 な薄膜積層による高集積化が期待されてい る. しかし TMDC に対するドーピング方法は確立されておらず、特に p型におけるコンタクト特性が良くないため p型ドーピング方法の確立と、ドーピングによるコンタクト 特性の改善が課題となっていた. これまでの 研究より、WSe<sub>2</sub>上への F6-TCNNO 成膜によ って WSe2に対するp型ドーピング効果とト ンネル電流によるコンタクト特性の改善が 確認されている. しかしその後のデバイス 作製においては F6-TCNNQ の成膜状況は重 要であるものの評価がなざれていなかった. ドーパント分子の不均一性はキャリア密度 の違いを生み、FET 性能に影響を与えることになる。そこで本研究では、F6-TCNNQ 成膜時の基板温度や,その後の真空アニール 温度,時間などをパラメータとした成膜状況 について、原子間力顕微鏡(AFM)による表 面観察と FET 特性評価をもとに、F6-TCNNQ 単分子層形成について議論する.

### 2. 実験

機械的剥離によって得られた数層の WSezに対してオゾンクリーニング5分行い表面清浄化を図った。その後真空管状炉内で F6-TCNNQ を  $160^{\circ}$ C 20 分加熱し昇華させ,同一管内の WSez結晶に対して成膜した。その際 WSez 側の基板温度を一定温度に維持することで,成膜状況の再現性を確保している。その後成膜した WSez結晶に対して真空アニールを行い,真空アニール前後での成膜状況の変化について AFM を用いて確認した.

### 3. 結果・考察

Fig. I(a)は、F6-TCNNQ を 160°Cで 20 分加熱 し昇華させ、 $WSe_2$  基板を 150°Cで 40 分維持し 成膜したも際の AFM 像である. ラインプロファイル青に示すように、F6-TCNNQ が成腐されている部分と成膜されていない部分の子が単層で平面状に成膜されていると考えらよる. 一方でラインプロファイル緑に示すように、成膜されている部分の上にさらにわからに、成膜されている領域があることがわらく(自く)なっている領域があることがわった。この領域の高さは 1.5 nm 程度であり、二層 以降のF6-TCNNQについては分子が立つようにして成膜される様子が確認された. Fig. 1(b)は、(a)に対して 180°C 1h 真空アニールを

行った後の AFM 像である. (a)から(b)への変化に着目すると分子膜の均一性が向上していることが確認できた. 一方でラインプロファイルに着目すると 1~1.5nm 程度の凹凸が確認され, 平坦性については改善が必要であることが示唆された.

Fig. 1(c)は, (b)に対してさらに200℃ 1h真空アニールを行った後の AFM 像である. (c)では所々に分子が乗っていない穴が空いている様子が確認された. 一方で分子が成膜されている領域の平坦性については向上しているため, F6-TCNNQ 成膜段階での成膜量を調節するなどの工夫により, 単分子層で 100%の被覆率を目指して研究を進めている.

#### 4. 結論

WSe<sub>2</sub>上に成膜した F6-TCNNQ に対して真空 アニールを行うことで平坦性と均一性の向上 が確認されており、単分子層を実現できる可 能性が示唆されている.一方で真空アニール によって新たに生まれてしまう穴については F6-TCNNQ 成膜段階での成膜量を調節するこ とや穴のできた領域に再成膜することによっ て改善できるのではないかと考えられる.

#### 謝辞

本研究は東京エレクトロン(株)の支援を受けて行われた.

#### 参考文献

[1] L. Wang, et al., Science, 342, pp.614 (2013).[2] K. Matsuyama, et al., ACS Appl. Mater.

[2] K. Matsuyama, et al., ACS Appl. Mater. Interfaces, **14**, pp.8163-8170 (2022).

Fig. 1.  $1\mu m \times 1\mu m$  AFM images of F6-TCNNQ on WSe<sub>2</sub>. F6-TCNNQ deposition conditions; F6-TCNNQ sublimation at 160°C for 20 min and WSe<sub>2</sub> substrate 150°C 40 min. (a) As deposited. (b) After vacuum annealing at 180°C for 1h. (c) After vacuum annealing at 200°C for 1h for (b).

## 二次元半導体材料の界面準位密度評価手法

## The analytical method for evaluation of interface state density of 2D semiconductor channel materials

筑波大学数理物質科学研究群 °(M1)佐藤 優, 蓮沼 隆 Univ. of Tsukuba, °Sato Masaru and Ryu Hasunuma E-mail: s2420293@u.tsukuba.ac.jp

半導体素子の微細化により顕著になる短チャネル効果を抑制するために二次元半導体材料をチャネルとすることが注目されている。 二次元半導体材料は、理想的には隣接する物質との間に共有結合を持たないため、界面準位が存在しないことが期待されるが、実際は準位が存在することが報告されている。

従来の半導体デバイスでは界面準位密度を評価する際、Hi-Lo C-V 法が一般的に用いられているが、二次元半導体はその薄さにより空乏層が広がらないために別の方法が必要である。我々は二次元半導体材料の界面準位密度を定量的に測定する方法を考案したので報告する。

今回考案した方法では、Si/SiO2 基板の SiO2 上に二次元半導体膜を形成し、その上に接地 したソース電極と浮遊したドレイン電極を堆 積した FET を用いる。デバイスのオン・オフ 状態を繰り返すために Si 基板 (バックゲー ト)にパルス電圧を印加する。オン状態では ソース電極からキャリアが流入し、オフ状態 ではそのキャリアがソースに戻っていく。浮 遊したドレイン電極には電圧計を接続し、チャネル電位をモニターする。デバイスがオン 状態になったときのキャリアのチャネルへの 流入は、ソース電極におけるコンタクト抵抗 およびチャネル抵抗とゲート酸化膜容量とで 決まる時定数で表現される充電現象といえる。一方、オフ状態になったときはこれら抵抗成分に、界面準位に捕獲されたキャリアが放出される際の抵抗成分が加わった時定数で表現される放電現象となる。チャネル電位は充放電過程に応じて変化するので、オン状態およびオフ状態でのチャネル電位の時間変化から、界面準位からの放出過程の時定数を見積もることができ、界面準位のエネルギー分布を調べることができると考えられる。また、電位変化の大きさから準位密度の算出が可能であることが期待される。

本手法では基本的にオン状態での電位変化とオフ状態での電位変化の時定数の差を基に界面準位分布を評価するため、チャネル抵抗とコンタクト抵抗をできるだけ小さくすることが求められる。そのため、短チャネルかつソース面積が大きいデバイスを用いる必要がある。あるいは、あらかじめこれらの抵抗成分を明らかにしたうえで解析をする必要がある。

当日は測定結果も含め、報告する。

本研究は「電波有効利用研究プログラム\_革 新的情報通信技術(Beyond 5G)基金事業」 および「未来社会創造事業(探索加速型)」の 支援を得て遂行された。

## 層状ヒ化ゲルマニウム膜の熱酸化による膜厚制御

Thickness control of layered germanium arsenide film via thermal oxidation 信州大工¹, 信州大 先鋭材料研² ○蓮見歩太¹, 浦上法之¹², 橋本佳男¹²

Shinshu Univ. <sup>1</sup>, Shinshu Univ. RISM <sup>2</sup> Ayuta Hasumi<sup>1</sup>, Noriyuki Urakami<sup>1,2</sup>, Yoshio Hashimoto<sup>1,2</sup> E-mail: urakami@shinshu-u.ac.jp

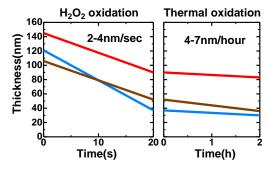

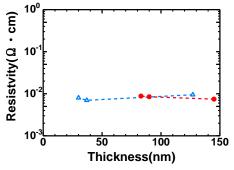

ゲルマニウム(Ge)とヒ素(As)の化学量論組成比(V/IV)が 1 の化合物(GeAs)は、安定な層状物質であり正孔が電気伝導を担う p 型半導体である[1]。そのため、導電制御に関する汎用的な手法が確立されていない二次元物質において新たな材料の選択性を与えうる[2]。しかし、GeAs は 100 nm 以下に薄膜化にすることにより、接触抵抗の極端な増加が示唆される[3]。前回の講演会において、過酸化水素水による GeAs の酸化と純水によるその酸化膜除去の素子作製工程を提案し、その接触抵抗を悪化させない層数制御手法について報告した[4]。しかし、薄膜化した際の層数の制御性能が向上できず、数層単位での制御には不向きであった。本報告では、前述した工程に加えて酸素雰囲気下において GeAs を加熱し表面酸化を行う事で薄膜化後の精密な層数制御について検討した。

GeAs 膜の作製には、固体原料を用いた物理気相輸送法を用いた[2,3,4]。作製した GeAs 膜をサファイア基板上に転写し、フォトリソグラフィとリフトオフ工程により金の二端子電極を面内方向に沿って付与した。作製した素子は希釈した過酸化水素水に入れて膜表面を酸化し、純水によって酸化物を除去することで GeAs 膜を薄膜化した。この工程によって GeAs と Au 電極の接触部分を厚膜に維持しながらチャネル部の薄膜化を実現した(図1左)。

その後、GeAs 薄膜を酸素雰囲気下において 350 °C で二時間加熱し表面を再度酸化させ、純水により酸化膜の除去を行うと微少な膜厚の減少を実現した(図 1 右)。この工程において、チャネル部の膜厚の減少に伴う接触抵抗の大幅な増加は見られず、さらなる GaAs の薄膜化技術として有用であることが示された(図 2)。

[謝辞] 本研究の一部は、村田学術振興財団(M23 助自 114)の援助を受けて実施された。

[1] S. Yang, et al., *Advanced Functional Materials* **28**, 1707379 (2018). [2] Y. Suzuki, et al., *Materials Letters* 283, 128748 (2021).[3] S. Kagami et al., *CrystEngComm* **24**, 4085 (2022). [4] 蓮見歩太 他、第 71 回応 用物理学会春期学術講演会 予稿集、23p-31B-14.

**Fig1** Film thickness depending on H<sub>2</sub>O<sub>2</sub> and thermal oxidation times.

**Fig.2** Film thickness dependence of resistivity before and after oxidation.

## 二次元層状金属 NbS2 の実効仕事関数評価

NbS<sub>2</sub> as a TMDC metal with a high effective work function 産総研 先端半導体研究センター<sup>1</sup>, 明治大 <sup>2</sup>, 明治大 MREL<sup>3</sup> °堀 幸妃 <sup>1,2</sup>, 張 文馨 <sup>1</sup>, 入沢 寿史 <sup>1</sup>, 小椋 厚志 <sup>2,3</sup>, 岡田 直也 <sup>1</sup>

AIST SFRC<sup>1</sup>, Meiji Univ. <sup>2</sup>, MREL<sup>3</sup> °K. Hori<sup>1, 2</sup>, W. H. Chang<sup>1</sup>, T. Irisawa<sup>1</sup>, A. Ogura<sup>2, 3</sup>, N. Okada<sup>1</sup> E-mail: hori-koki@aist.go.jp

【背景】半導体の遷移金属カルコゲナイド(TMDC)は、数原子層の厚さで高いキャリア移動度を有し、微細 CMOS のチャネル材料として期待されている。しかし、微細トランジスタの高性能化には、ソース/ドレイン(S/D)部でのコンタクト抵抗低減が必要である。我々は、TMDC チャネル向けのコンタクト材料として、金属の TMDC に着目しており、これまでに、Nb を 600 ℃以上の  $H_2S$  熱処理することで、二次元層状金属の  $NbS_2$  を形成できることを示している[1]。第一原理計算からは、 $NbS_2$  が  $WSe_2$  とヘテロ積層構造を形成することで、低抵抗コンタクトの実現が予測されている[2]。現に、我々は、 $WSe_2$  チャネルに対して、 $NbS_2$  を S/D 部のコンタクト材料として利用することで、 $WSe_2$ -pFET のオン電流が向上することを報告している[1]。この性能向上の要因を明らかにするために、本研究では、熱酸化膜(SiO2)/Si 基板上に  $NbS_2$  を  $H_2S$  熱処理により形成して、MOS キャパシタを作製し、フラットバンド電圧  $V_6$  から  $NbS_2$  の実効仕事関数(eWF)を調べた。

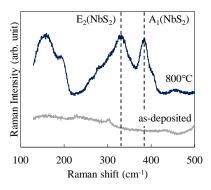

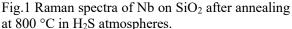

【実験】 $SiO_2$  (膜厚 t=24-98 nm)/n-Si (~5  $\Omega$ ·cm)基板上へ Nb (t=3 nm)を蒸着法で形成し、 $H_2S$  雰囲気下の熱処理(圧力: 50 kPa、熱処理時間: 10 min、熱処理温度:  $T_a=800$  °C)により NbS2 を作製した。ラマン散乱分光法により NbS2 の結晶性を評価し、次に、NbS2 上に蒸着法で Au 電極(t=50 nm)を形成して MOS キャパシタを作製し、容量-電圧(C-V)特性の  $V_{fb}$ より eWF を算出した。

【結果】 $SiO_2$ 上の Nb は  $H_2S$  と反応することで、NbS<sub>2</sub>の  $E_2$ モード (330 cm<sup>-1</sup>) と  $A_1$ モード (385 cm<sup>-1</sup>) を示した (Fig.1)。この NbS<sub>2</sub>を電極に用いたキャパシタでは、NbS<sub>2</sub>の膜厚を 5-20 nm で変化させても、 $V_{fb}$ 、および、蓄積領域における C の値はそれぞれ一定の値を示した。これは、NbS<sub>2</sub>が、寄生容量成分が無く電極として機能していることを示している。また、キャパシタの  $SiO_2$  膜厚依存性より、NbS<sub>2</sub>の eWF は 4.8 eV を示した (Fig. 2)。この値は、Au 電極の eWF = 4.6 eV よりも高く、NbS<sub>2</sub>は Au よりも高い仕事関数を有している。一方、NbS<sub>2</sub>の固有の仕事関数は~6.2 eV であり [2]、 $SiO_2$ 上の NbS<sub>2</sub>の MOS キャパシタの結果と対応しない。この理由は、WSe<sub>2</sub>上の NbS<sub>2</sub>が良好な結晶性を示した結果[1]とは対照的に、 $SiO_2$ 上の NbS<sub>2</sub>が理想的な結晶になっていない可能性を考えている。

このような高い仕事関数の二次元層状金属は WSe<sub>2</sub>-pFET のコンタクト材料として有望である。これまでに、NbS<sub>2</sub> コンタクトの WSe<sub>2</sub>-pFET では、高い仕事関数(~5.0-5.3 eV)を有する Ni コンタクよりも、オン電流が向上することが分かっている[1]。Ni コンタクトの場合には、Ni/WSe<sub>2</sub> 界面でフェルミレベルが WSe<sub>2</sub> のミッドギャップ近傍にピンニング[3]することで、正孔障壁高さが高くなっており、NbS<sub>2</sub>/WSe<sub>2</sub> 界面では、van der Waals を介したヘテロ接合を形成することで、フェルミレベルピンニングが緩和され、Ni コンタクトよりも正孔障壁高さが低減していると考える。

【まとめ】二次元層状金属である  $NbS_2$  は熱酸化膜上で 4.8~eV の高い eWF を示した。 $NbS_2$  は TMDC チャネル pFET 向けのコンタクト材料として期待できる。

Fig.2 The flat-band voltage  $V_{\rm fb}$  of the NbS<sub>2</sub> as a function of the SiO<sub>2</sub> thickness.

【謝辞】本研究の一部は、JST-MIRAI (JPMJMI22708192)、科研費 (JP23K26151)の助成を受けて実施された。

【参考文献】[1] 堀 幸妃 他, 第 71 回応用物理学会春季学術講演会, 25a-71B-9 (2024). [2] X. Ding et. al., Phys. Rev. Applied. 12, 064061 (2019). [3] D. S. Schulman et. al., Chem. Soc. Rev. 47, 3037 (2018).

## TMDC 膜質の In-situ-ALD-Al<sub>2</sub>O<sub>3</sub> カバー成膜時基板温度依存性

TMDC crystallinity on substrate temperature in in-situ-ALD-Al<sub>2</sub>O<sub>3</sub> cover formation 東工大 <sup>○</sup>布施太翔,松永尚樹,岡村俊吾,黒原啓太,伊東壮真,野澤俊輔,白倉孝典,若林整 <sup>°</sup>Taiga Fuse, N. Matsunaga, S. Okamura, K. Kurohara, S. Ito, S. Nozawa, T. Shirokura and H. Wakabayashi, Tokyo Institute of Technology, E-mail: fuse.t.ad@m.titech.ac.jp

【緒言】遷移金属ダイカルコゲナイド(TMDC) は薄膜においても高い移動度を持つため、次世代半導体として期待されている $^{[1]}$ 。一方、 $Al_2O_3$  絶縁膜の形成で用いられる原子層堆積法 (ALD)では、 $H_2O$  プリカーサーによって TMDC 膜を酸化することが報告されている $^{[2]}$ 。そこで in-situ-ALD による  $Al_2O_3$  カバー成膜について、TMDC 膜質の基板温度依存性を調査した。

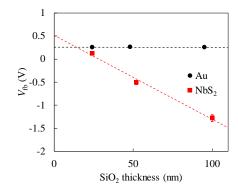

【方法】SiO<sub>2</sub>(700 nm)/n-Si 基板上に、1.2-nm 厚の  $MoS_2$  膜を RF パワー50 W, 基板温度 450℃, 圧力 0.55 Pa でのスパッタ法により成膜した後、4.5-nm 厚の  $Al_2O_3$  膜をトリメチルアルミニウム(TMA)と  $H_2O$  を用いる in-situ-ALD により基板温度 150-350℃ で堆積した。ここで 150℃未満や 350℃以上では、ALD- $Al_2O_3$  膜は残留物により誘電率が劣化することを考慮した [3,4]。

【結果】Fig. 1 にラマン分光法により測定した MoS<sub>2</sub> 薄膜ピークの半値幅の Al<sub>2</sub>O<sub>3</sub> 成膜温度依 存性を示す。また Table 1 に、各温度における 半値幅の標準偏差を示す。これらの図表より、 250℃ 以上で半値幅が減少することがわかる。 これは、基板加熱によるマイグレーションの効 果[5]が支配的になり、 $MoS_2$  膜質が向上したた めと考えられる。一方、250℃未満でも半値幅 を低減でき、特に 150°C で半値幅の平均と標準 偏差が最も小さくなることがわかる。これは、 低温化で $H_2O$ による $MoS_2$ 膜の酸化[2]が抑制さ れたためと考えられる。ここで、150℃未満で は TMA が分解されないことから Al<sub>2</sub>O<sub>3</sub> 膜の膜 質が劣化して誘電率が顕著に減少するため[3]、 MoS<sub>2</sub> 膜上での ALD-Al<sub>2</sub>O<sub>3</sub> 成膜の基板温度は 150℃程度が適切であると考えられる。

【結言】 $MoS_2$ 薄膜上に $Al_2O_3$ 膜を堆積する際、 基板温度が  $150^{\circ}C$  のときに小さい  $MoS_2$  薄膜の 半値幅が得られた。今後は他の TMDC 薄膜に ついても同傾向が観察されるかを調査する。

Fig. 1: PVD MoS<sub>2</sub> film full-width half maximum of the Raman spectrum on substrate temperature.

Table 1: Standard deviation values of MoS<sub>2</sub> film FWHM for each substrate temperature from Fig. 1.

| Temperature [°C] | Standard deviation [cm <sup>-1</sup> ] |  |

|------------------|----------------------------------------|--|

| 150              | 0.399                                  |  |

| 200              | 0.748                                  |  |

| 250              | 1.030                                  |  |

| 300              | 1.230                                  |  |

| 350              | 0.642                                  |  |

【謝辞】本研究の一部は X-nics 半導体創生拠点形成事業 (JPS011438) 及び JSPS 科研費 (20H05880)の助成を受けた。

#### 【参考文献】

- [1] W. Zhang, et al.: Nano Res., 7(12), 1731 (2014).

- [2] J.G. Song, et al.: ACS Appl. Mater. Interfaces, 8, 41, 28130 (2016).

- [3] S. Kim, et al.: Sci. Rep, 12, 5124 (2022).

- [4] M.D. Groner, et al.: Thin Solid Films, **413**, **1-2**, 186 (2002).

- [5] R. Zhang, et al.: Surf. and Coat. Tech., **401**, 126215 (2020).

## 局所的な曲率構造を有するヤヌス WSSe 面内へテロ系のエネルギー論と 電子状態

Energetics and electronic structures of corrugated in-plane heterostructures of Janus WSSe

## 筑波大数理 ○丸山実那, 岡田 晋, 高 燕林

Univ. Tsukuba, ,  $^{\circ}$ Mina Maruyama, Susumu Okada, Yanlin Gao

E-mail: mmaruyama@comas-tsukuba.jp

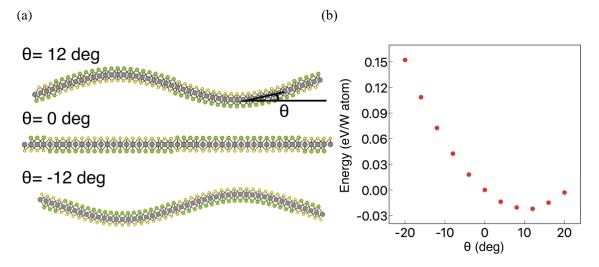

遷移金属カルコゲン化合物(TMD)は、遷移金属原子とカルコゲン原子からなる三原子厚の原子層物質である。TMD の電子状態は構成原子種に依存した多様性を示すことから、構造によるTMD系の電子状態の制御が着目されている [1]。加えて、TMDの面鉛直方向の高い柔軟性は、シワや折り畳みなどの局所的なナノ構造構築を可能とし、それによる電子状態の変調が理論的に予言されている [2]。本研究では、密度汎関数理論に基づく第一原理計算手法を用いて、図(a)で示す局所的な曲率構造を有するヤヌス WSSe 面内へテロ構造のエネルギー論と電子状態の解明を行なった。

図(b)に曲率構造を有するヤヌス WSSe 面内へテロ構造のエネルギーの曲率角度依存性を示す。 曲率の内側が S、外側が Se、かつ  $\theta=12^\circ$  の構造が最もエネルギー的に安定であることを明らか にした。他方、曲率の外側が Se、内側が Se の構造は、曲率角度が大きくなるにつれてエネルギー 的に不安定な構造となる。曲率構造を有するヤヌス WSSe 面内へテロ構造の電子状態は、局所的 な構造に依存した変調を示すことを明らかにした。

- [1] Y. Gao and S. Okada, Appl. Phys. Express 16, 075004 (2023).

- [2] Y. Gao, et al. Jpn. J. Appl. Phys. 62, 015001 (2023).

図:曲率構造を有するヤヌス WSSe 面内へテロ構造の(a) 最適化構造、(b) エネルギーの曲率 角度依存性。黄色、緑、灰色は硫黄、セレン、タングステンを表す。

## CVD-monolayer MoS<sub>2</sub> MIS キャパシタにおける接触電極の形状依存性

Dependence of contact electrode shape on Ti/h-BN/CVD-monolayer MoS2 interface 千葉大·エ¹,東京都立大²,○鶴岡 大樹¹,遠藤 尚彦²,宮田 耕充²,青木 伸之¹,柯 梦南¹ Chiba Univ.¹, Tokyo Metropolitan Univ.², ○Daiki Tsuruoka¹, Takahiko Endo², Yasumitsu Miyata², Nobuyuki Aoki¹, Mengnang Ke¹,

E-mail: mke@chiba-u.jp

#### 1. はじめに

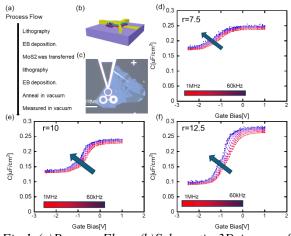

近年,シリコンを用いた半導体デバイスに はスケーリングの限界がきており,それに代 わる新たな材料として遷移金属ダイカルコ ゲナイド(TMDC)が挙げられる.TMDC は2 次元半導体であり短チャネル効果を抑制で きることから FET としての研究が非常に盛 んである[1].しかしながら,MIS界面の研究は 少ない[2][3].なぜなら2次元半導体ゆえの MIS キャパシタの測定の難しさがある.今回 は2次元材料であり,高い平坦性と結晶性を 持つことから広く使われている絶縁体の六 方晶窒化ホウ素(h-BN)と n 型半導体であ り、TMDC の中で最も研究されている素材で ある 2 硫化モリブデン(MoS<sub>2</sub>)によって CVDmonolayer MoS<sub>2</sub> MIS キャパシタを作製し,接 触金属の面積差による静電容量特性につい て,議論・考察する.

#### 2. 実験

アセトンとイソプロピルアルコール(IPA) を用いて洗浄したガラス基板上に,電子線リ ソグラフィーを用いてリング型の Bottom パ ターンを描画し(R=15 um, r=7.5,10,12.5 um),EB 蒸着を用いて Bottom 電極(Cr/Au:10 nm/20 nm)を作製した.次に h-BN を機械的剥 離によって用意し、基板に転写した後、テープ による有機残渣を取り除くためにAr/H2ガス 雰囲気下にて低圧アニール(500 ℃,60 min)を 行った.その後 CVD 成膜により得られた単 層の MoS<sub>2</sub>と h-BN をポリジメチルシロキサ ン(PDMS)レンズとポリビスフェノール・ ア・カーボネート(PC)フィルムを用いてド ライトランスファー[4]しBottom電極上に積 層させた.そして電子線リソグラフィーにて 円形の Top パターンを描画し(R=15 um),EB 蒸着にて Top 電極(Ti/Au:10 nm/50 nm)を作製 した.その後真空中にて静電容量の測定を行 い,さらに真空アニール(250 °C,60 min)を行 った後同じ測定を行った.

#### 3. 結果・考察

Fig.1(d)-(f)は各デバイスについて真空中にて測定を行った結果である.各デバイス間について見ると depletion 時に明らかな容量差が観測された.これらの要因として考えられるものは,・MIS 界面が MoS2/接触電極界面が表裏で隣接しているため,接触金属由来の界面準位密度により電子がピニングされるとしての寄生容量があることが考えられるしての寄生容素すべく,コンダクタンス法にしたの寄生容素すべく,コンダクタンス法にしたが,ピークらしきものは存在するが,周波数によりシフトが起こらず,界面準位密度による

ものと断定できていない.界面準位密度によるコンダクタンスピークがなぜ見えてこないのかについては様々な理由が考えられる.例えば,構造中にて発生した結晶のひずみであったり,ピニングにより MIS 界面付近でのバンドが小信号応答できなかったりなどの考察が挙げられる.

#### 4. 結論

今回はTi/h-BN/CVD-monolayer MoS<sub>2</sub> MISキャパシタを作製し、それらの接触電極の構造を変化させることで、デバイスにどのような変化がもたらされるかについて実験を行った、このデバイスでは、コンダクタンス法を用いた界面準位密度の測定までには至らなかったが、予備実験として行った上下構造を変え、リング型の接触電極を最後に蒸着する方法では、コンダクタンスピークが CVD-monolayer MoS<sub>2</sub>にて観測できていることから、これらの構造の違いについて比較検討し、どのプロセスが適当なのかを検討していく必要がある.

#### 5. 謝辞

本研究は JSPS 科研費 JP23K13361,東京エレクトロン (株),服部報公会及び日本科学協会笹川科学研究助成の支援を受けている.

#### 6. 参考文献

[1] Jia, X, et al. ACS Applied Materials & Interfaces 16.13 (2024): 16544-16552. [2] Gaur, A, et al. 2D Materials 6.3 (2019): 035035. [3] Takenaka, M., et al. 2016 IEEE International Electron Devices Meeting (IEDM). IEEE, (2016). [4] T. Iwasaki et al. ACS appl. Mater. Interface, 8533-8538 (2020)

Fig.1 (a)Process Flow, (b)Schematic 3D image of devices, (c)optical image of devices. And differences in capacitance characteristics between devices. (d)-(f)

## 熱電応用のための WTe2 ナノワイヤの合成及び性能評価

# Synthesis and performance evaluation of WTe<sub>2</sub> nanowires for thermoelectric applications

北大院総化 <sup>1</sup>, 北大院工 <sup>2</sup> O(M1C)伊瀬 亘 <sup>1</sup>, 横倉 聖也 <sup>1,2</sup>, 和泉 廣樹 <sup>1,2</sup>, 島田 敏宏 <sup>1,2</sup>

CSE. <sup>1</sup>&, Eng. <sup>2</sup> Hokkaido Univ., <sup>°</sup>Wataru Ise <sup>1</sup>, Seiya Yokokura <sup>1,2</sup>, Hiroki Waizumi <sup>1,2</sup>, Toshihiro Shimada <sup>1,2</sup>

E-mail: ise.wataru.p4@elms.hokudai.ac.jp

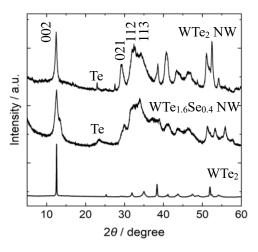

【緒言】熱電変換は熱エネルギーと電気エネルギーを相互に変換できる技術であり、自動車や工場などで発生する廃熱を利用して発電することで温室効果ガスを削減し、クリーンなエネルギーを生み出すことが可能なため、環境保護の観点から期待されている。発電を目的とする場合に熱電材料に求められる性能は高く、変換効率の向上が最優先事項とされている[1]。本研究では重元素を含む遷移金属ダイカルコゲナイドに注目し、ナノワイヤ状のWTe2とWTe1.6Se0.4の合成を試み、熱電性能を評価した。

【実験】ソルボサーマル法により粉末状の $W_{18}O_{49}$ ナノワイヤを合成し、 $NaBH_4$ 、Te、Se とともに真空下で封じたガラス管中で加熱することにより、 $WTe_{2-x}Se_x$ ナノワイヤを得た。得られた試料はXRD、TEM により構造解析し、ホール測定、ゼーベック係数測定により性能評価した。

【結果・考察】TEM 観察で太さ約 25 nm のナノワイヤを確認した。XRD はナノワイヤ試料のピークがブロードであることを示し、結晶子サイズが非常に小さいことが確認された(Figure1)。WTe<sub>1.6</sub>Se<sub>0.4</sub>ナノワイヤのXRD は (002) 面のピークに肩が出ており、Se イオンが置換した成分の存在が示唆された。ナノワイヤ試料のXRD(2 $\theta$ =23.1°)に見られる単体 Te の除去が今後の課題となる。Se を添加することでキャリア濃度が増加し、それに伴いゼーベック係数の値が低下した(Table 1)。得られた試料の出力因子は大きくないが、移動度が高いことから適切なドーピングを行い、キャリア濃度を調整することによって熱電性能の向上が期待できる。

Figure 1 XRD of nanowire samples and WTe<sub>2</sub> crystals

Table 1 Thermoelectric performance of samples

| sample                               | Seebeck coefficient | Mobility             | Carrier concentration | Power factor          |

|--------------------------------------|---------------------|----------------------|-----------------------|-----------------------|

|                                      | $(\mu V/K)$         | $(cm^2/Vs)$          | (cm <sup>-3</sup> )   | $(W/mK^2)$            |

| WTe <sub>2</sub>                     | 192.7               | $5.28 \times 10^{3}$ | $2.07 \times 10^{16}$ | $6.51 \times 10^{-5}$ |

| WTe <sub>1.6</sub> Se <sub>0.4</sub> | 175.5               | $2.78 \times 10^{3}$ | $4.72 \times 10^{16}$ | $6.47 \times 10^{-5}$ |

<sup>[1]</sup> Zhang, Q.H, et al., Adv. Eng. Mater., 18, 194-213, 2016