Tadayoshi MIFUNE, Shigeyuki OCHI, and Yasuo KANO

SONY Corporation Research Center

174 Fujitsukacho, Hodogaya-ku, Yokohama, JAPAN 240

We report an improved structure of a charge-coupled device by placing high resistive material between transfer gate electrodes on gate oxide.

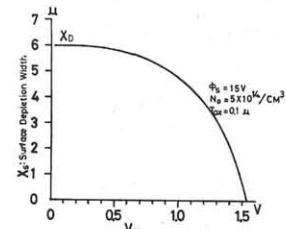

In a CCD with gate electrodes of single layer, the electrode separation is several micrometers, and a potential barrier is inclined to arise under  $\text{SiO}_2$  of these inter-electrode gaps. For the complete transfer of charge in a CCD, such a potential barrier must be reduced. To satisfy this requirement, we have to place the electrodes sufficiently close. Where a transferring charge is a hole, an existence of interface states makes the potential barrier larger, and depletion layer width at the surface is reduced as compared with that of the interior of the Si substrate. In Fig. 1, a reduction of a surface depletion layer vs  $V_{th}$  is shown by a simple calculation. This condition requires closely spaced electrodes and, accordingly, more difficult photolithographic technique.

Actually we have hardly got a CCD in action on a condition of 2.5 v threshold voltage and 3  $\mu\text{m}$  inter-electrode gap width on a  $10\Omega\text{-cm}$  N-type substrate. However, when the surface of  $\text{SiO}_2$  is contaminated (for instance, a hydrated surface of phosphorous silicate glass), the dirt adhered to the surface polarizes and forms a temporary electrode which eliminates the potential barrier, then the CCD gets in operation. But this polarized layer has a large time constant and influences undesirably on the charge behavior.

Metallization of a single layer is a simple method for the CCD fabrication unless before mentioned situation at a gap makes any trouble.

We introduce a high resistive material on  $\text{SiO}_2$  of inter-electrode gap, whose potential is controlled by the difference of the adjacent electrodes, and maintains a certain potential which is generally

Fig. 1

Reduction of Depletion layer at Surface vs  $V_{th}$

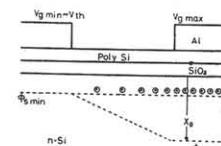

Fig. 2

Cross Section View

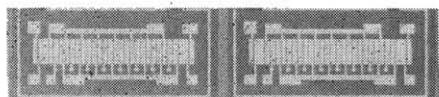

Fig. 3

3 Phase 8 Bit CCD

above  $V_{th}$ . Fig. 2 shows a cross section view of this CCD with polycrystalline silicon as a high resistive material. The device has been fabricated on a nominal  $10\Omega\text{-cm}$  N-type substrate with (100) orientation. A gate oxide film of  $0.1\text{ }\mu\text{m}$  thick was grown at  $1100^\circ\text{C}$  in dry  $\text{O}_2$ , then polycrystalline silicon was deposited chemically at  $670^\circ\text{C}$  followed by evaporation directly over it.

Thus we constructed a 3 phase 8 bit CCD with a gate area of  $250 \times 50\text{ }\mu\text{m}^2$  as shown in Fig. 3.

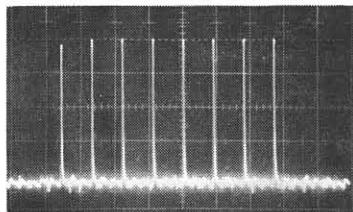

Fig. 4 Characteristic

100 $\mu\text{s}/\text{div}$

0.1 V/div

Fig. 5

Single Line Scanner

Fig. 6

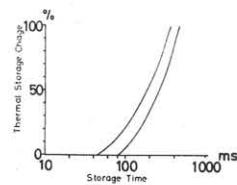

Thermal Storage Time

A characteristic of the shift register at 11.1 kHz is shown in Fig. 4. Fig. 5 shows our application of this device to a single line scanner as an image sensor. Fig. 6 shows its thermal charge generation time.

Stable operation of a CCD with inter-electrode gap of  $5\mu\text{m}$  and a  $V_{th}$  of 4 v was achieved.

We also achieved in reducing the severe requirements on photolithographic technology and the surface condition.

#### Acknowledgement

We would like to thank Dr. K. Wakamiya, Dr. Yoshida, Mr. T. Shimada for appropriate advices, and Mr. H. Ogasawara and others for processing the test devices.

#### References

1. Boyle, W.S., and Smith, GE. BSTJ 49 No. 4 (Apr. 1970) pp587

2. N. Suzuki and H. Yanai SSD 71-65(1972-02)

3. R.H. Krambeck BSTJ 50 No. 10 (Dec. 1971) p3169