# Organic ferroelectric gate FET memory using high-mobility rubrene thin film

Takeshi Kanashima<sup>1</sup>, Yuu Katsura<sup>1</sup>, and Masanori Okuyama<sup>2</sup>

<sup>1</sup> Division of Advanced Electronics and Optical Science, Department of Systems Innovation, Graduate School of Engineering Science, Osaka University, Machikaneyama 1-3, Toyonaka, Osaka 560-8531, Japan

Phone: +81-6-6850-6332 E-mail: kanashima@ee.es.osaka-u.ac.jp

<sup>2</sup> Institute for NanoScience Design, Osaka University, Machikaneyama 1-3, Toyonaka, Osaka 560-8531, Japan

## Abstract

Organic ferroelectric gate FET memory has been fabricated by using an organic semiconductor of rubrene thin film with high mobility and a gate insulating layer of P(VDF-TeFE) thin film. Rubrene thin film grown by physical vapor transport was prepared on spin-coated P(VDF-TeFE) thin film layer. A hysteresis loop caused by the ferroelectricity has been clearly observed in  $I_dV_g$  characteristics. The mobility of this organic ferroelectric gate FET is  $0.71 \text{ cm}^2/\text{Vs}$  which is 35 times larger than that using pentacene thin film. The drain current has been about one hundred times greater than that using pentacene.

## 1. Introduction

Recently, much attention has been paid to organic electronics, because organic devices have some advantages such as flexibility, light in weight, low preparation cost, and transparency. We have prepared organic ferroelectric gate FET memories using pentacene as an organic semiconductor and P(VDF-TeFE) as an organic ferroelectrics. Generally, ferroelectric gate FETs using an inorganic ferroelectric material need an insulating buffer layer between semiconductor and ferroelectric material to prevent the degradation of semiconductor-ferroelectric interface, because preparation of the inorganic-ferroelectric material need a high temperature for crystallization. Moreover, the quality of these buffer layers affects the retention property through depolarization field. On the other hand, preparation temperatures of organic ferroelectric and semiconductor materials are not so high. Thus, insulating buffer layer is not required in organic ferroelectric gate FET. However, the mobility of organic semiconductor prepared on organic ferroelectrics becomes small in comparison with the device without the ferroelectric material. Thus, wide gate width is required to obtain a large drain current, and the device size becomes to be large. So, the organic semiconductor having high mobility is required to be prepared on the organic-ferroelectric layer.

In this paper, ferroelectric gate FET memory using rubrene thin film with high mobility and P(VDF-TeFE) was prepared to increase the drain current, and was characterized.

## 2. Experimental

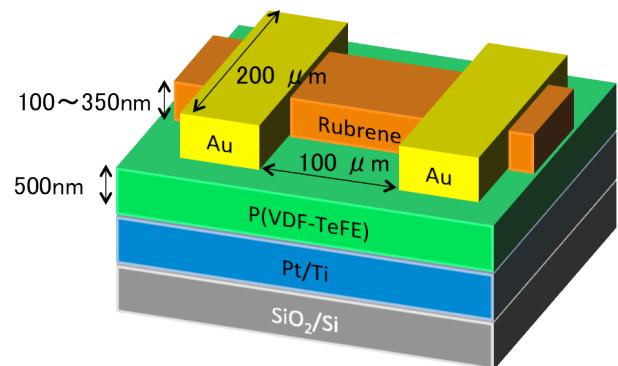

Figure 1 shows the schematic diagram of ferroelectric gate FET. P(VDF-TeFE) thin films were deposited on a Pt/Ti/SiO<sub>2</sub>/Si substrate by spin coating. Ti and Pt thin films were deposited successively on SiO<sub>2</sub>/Si substrate as gate electrodes by RF sputtering. P(VDF-TeFE) solution was spin-coated on Pt/Ti/SiO<sub>2</sub>/Si substrate at 1,500 rpm for 10 s, and dried at 170°C for 10 min. 80/20 mol% P(VDF-TeFE) was well solved in methyl-ethyl-ketone (MEK), and the concentration of P(VDF-TeFE) in MEK was 5 wt%. After spin coating, the thin films obtained were annealed at 170°C for 2 hours in air. Deposited P(VDF-TeFE) film thickness is 500 nm. Organic semiconductor rubrene thin film was separately grown at 225°C for 7 hours by physical vapor transport (PVT).[1]. Prepared rubrene thin films of 150-350 nm thickness were carefully placed on P(VDF-TeFE) thin film. An organic semiconductor pentacene thin film was deposited for the comparison with rubrene on the ferroelectric gate insulator of P(VDF-TeFE) using a vacuum evaporator. Au electrodes were formed as the source and drain electrodes. Gate width and length are 100 μm, respectively. The thin films and FET samples were characterized by XRD, AFM, and electrical properties such as  $I-V$  and  $P-E$ .

Fig. 1. Schematic diagram of ferroelectric gate FET using rubrene thin film and P(VDF-TeFE) ferroelectric thin film.

## 3. Results and discussions

XRD pattern of rubrene thin film was measured. Only the narrow (001) peaks that FWHM are about 0.05° are observed and the calculated lattice constant is 2.70 nm. This value agrees with the c-axis length of rubrene crystal.

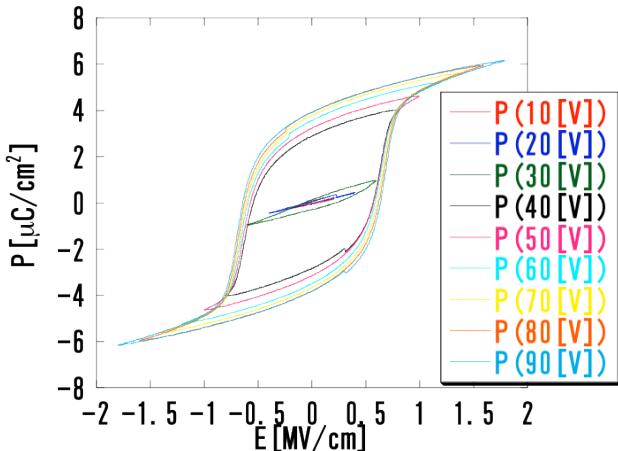

Moreover, very smooth surface is observed by AFM, and the height difference between the highest and lowest pixel is less than 1 nm on the area of 50  $\mu\text{m}$  square. Figure 2 shows the typical  $P$ - $E$  characteristics of P(VDF-TeFE) thin film. Saturated hysteresis loops are observed. Moreover, hysteresis loops indicate a good squareness.  $E_c$  is 0.64 MV/cm, and  $P_r$  is 3.9  $\mu\text{C}/\text{cm}^2$ . Surface roughness measured by AFM is 7.4 nm, and the flat surface is obtained.

Fig. 2.  $P$ - $E$  loops of P(VDF-TeFE) thin film. Film thickness is 500 nm, and measured frequency is 100 Hz.

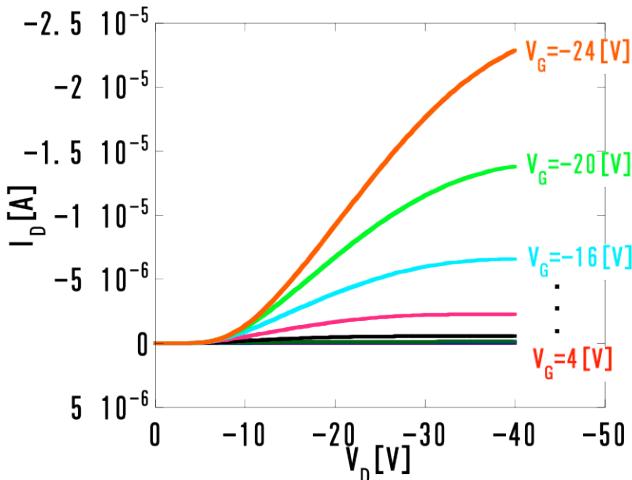

Figure 3 shows  $I_d$ - $V_d$  characteristics of ferroelectric gate FET. Since drain current is almost linearly proportional to drain voltage in the low-voltage region, this behavior is similar to that for a p-channel MIS FET fabricated using pentacene. Drain current becomes saturated at high drain voltage region. Moreover, the drain current is much larger than that prepared by using pentacene.[2] This is caused by the high mobility of the rubrene thin film, and reasonably good interface between rubrene layer and P(VDF-TeFE) layer can be formed by direct bonding.

Fig. 3.  $I_d$ - $V_d$  characteristics of ferroelectric gate FET using P(VDF-TeFE) thin film. Thicknesses of P(VDF-TeFE) and rubrene thin films are 500 nm and 130 nm, respectively.

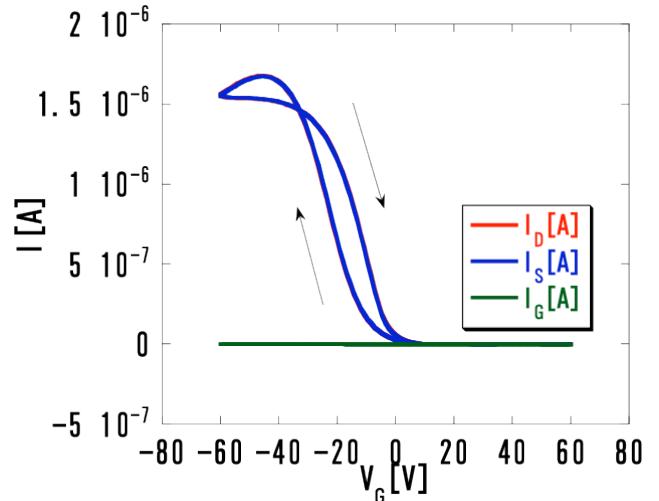

Figure 4 shows the  $I_d$ - $V_g$  characteristics. Clockwise hysteresis loop is clearly observed. The FET in which CYTOP (Asahi Glass Co.) thin film was used instead of P(VDF-TeFE) as a gate insulator was prepared in order to confirm that the hysteresis is caused by ferroelectricity. This FET has no hysteresis in  $I_d$ - $V_g$ , and the mobility is 0.79  $\text{cm}^2/\text{Vs}$ . So, it is thought that hysteresis is originated from the ferroelectric layer of P(VDF-TeFE). The memory window width originated by ferroelectricity of P(VDF-TeFE) is 9.6 V, and ON/OFF ratio at  $V_g = 0$  is 17. Calculated mobility of this FET is 0.71  $\text{cm}^2/\text{Vs}$ , and this value is 35 times larger than that fabricated by using pentacene thin film instead of rubrene thin film. However, the memory window width is not so large.

Fig. 4.  $I_d$ - $V_g$  characteristics of ferroelectric gate FET at  $V_d = -5$  V. Rubrene thickness is 130 nm.

#### 4. Conclusions

We have fabricated ferroelectric gate FET using rubrene thin film as a semiconductor and P(VDF-TeFE) as a ferroelectrics. Saturated  $P$ - $E$  loops and the flat surfaces are observed in the P(VDF-TeFE) thin film. Rubrene thin film having a flat surface is obtained, and ferroelectric gate FET can be prepared by placing the rubrene thin film on the P(VDF-TeFE) thin film. Typical  $I_d$ - $V_d$  characteristics are observed, and the hysteresis in  $I_d$ - $V_g$  characteristics originated by ferroelectricity is obtained. Moreover, the large drain current is obtained in comparison with the FET using pentacene, and the mobility of the organic ferroelectric gate FET using rubrene is 0.71  $\text{cm}^2/\text{Vs}$  which is enhanced 35 times larger than that using pentacene.

#### References

- [1] R. A. Laudise, Ch. Kloc, P. G. Simpkins, T. Siegrist J. Cryst. Growth, **187** (1998) 449

- [2] T. Watanabe, H. Miyashita, T. Kanashima and M. Okuyama, Jpn. J. Appl. Phys. **49** (2010) 04DD14.