## Low-temperature Microwave Annealing Process for Ge MOSFETs

Yao-Jen Lee<sup>1,6,\*</sup>, S.-S. Chuang<sup>2</sup>, C.-I. Liu<sup>3</sup>, F.-K. Hsueh<sup>1</sup>, P.-J. Sung<sup>1</sup>, C.-T. Wu<sup>1</sup>, C.-H. Lai<sup>4</sup>, Y.-M. Wan<sup>3</sup>, M. I. Current<sup>5</sup>, T.-Y. Tseng<sup>2</sup>

<sup>1</sup>National Nano Device Laboratories, Hsinchu, Taiwan; <sup>2</sup>Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan; <sup>3</sup>Department of Electronics Engineering, I-Shou University, Kaohsiung, Taiwan; <sup>4</sup>Department of Electronics Engineering, Chung Hua University, Hsinchu, Taiwan; <sup>5</sup>Current Scientific, San Jose, CA, USA; <sup>6</sup>Department of Physics, National Chung Hsing University, Taichung, Taiwan. Tel: +886-3-5726100-7793, Fax: +886-3-5722715, \*Email: [yjlee@ndl.narl.org.tw](mailto:yjlee@ndl.narl.org.tw)

### Abstract

Ge MOSFETs with all thermal processes preformed by microwave anneal (MWA) has been realized. The full MWA process is <390 °C. It significantly outperforms conventional RTA process in 3 aspects: (1) diffusion-less junction, (2) increased Cox and healed gate dielectric/channel interface, and (3) ultrathin 7.5nm nickel mono-germanide with lower sheet resistivity and contact resistivity. Compared to conventional RTA, the MWA gives 50% and 24% drive current enhancement for p- and n-MOSFET, respectively. These data show that the low temperature MWA is a promising thermal process technology for Ge MOSFETs manufacturing.

### Introduction

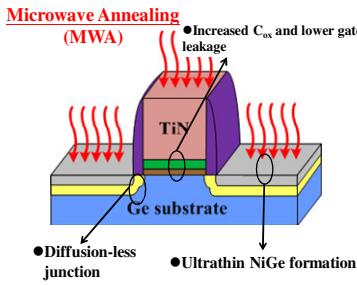

For dopant activation in Ge MOSFETs, RTA process >600 °C have been wildly adopted[1-2]. Such high temperature process causes the degradation of gate dielectric/ Ge channel interface, and results in severe dopant diffusion in source/drain region with Ge out-diffusion. In addition, for lowering the contact resistance to germanium, NiGe is the most promising candidate due to its low resistivity [3-4]. In order to thin down the thickness of NiGe, reducing the process temperature is necessary. However, a lower temperature results in a higher silicide resistance due to the small crystallite size. MWA is promising for achieving advanced Ge MOSFETs because of its unique low temperature due to apparent non-thermal energy transfer that is not yet fully understood[5]. The advantages for Ge MOSFETs with MWA are summarized in Fig. 1.

### Results and Discussion

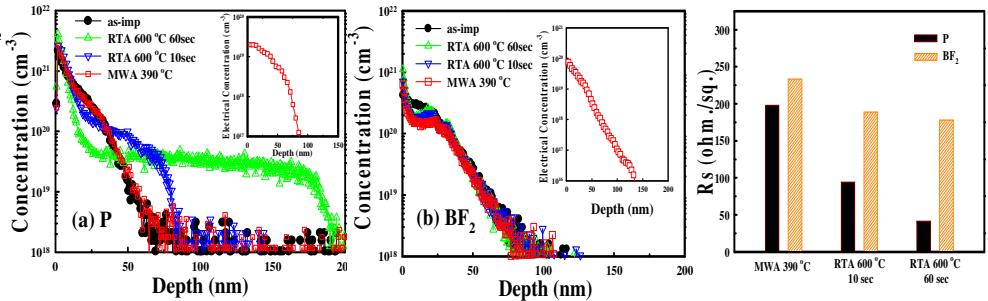

**Diffusion-Less Junction.** The n<sup>+</sup> and p<sup>+</sup> doping are introduced by P and BF<sub>2</sub> implants at a dose of  $1 \times 10^{15} \text{ cm}^{-2}$ , respectively. The peak temperature of dopant activation by MWA was 390 °C. Fig. 2(a) shows a significant diffusion of P after RTA and no P diffusion after MWA. For boron, comparable diffusion-less concentration profiles after MWA and RTA are observed and presented in Fig. 2(b). The activated levels of P and B after MWA are  $2 \times 10^{19} \text{ cm}^{-3}$  and  $7.5 \times 10^{19} \text{ cm}^{-3}$ , respectively. In Fig. 4, the deep junction of P formed by RTA results in the lower Rs. Thus, ultra shallow junctions can clearly be reached by the low temperature MWA.

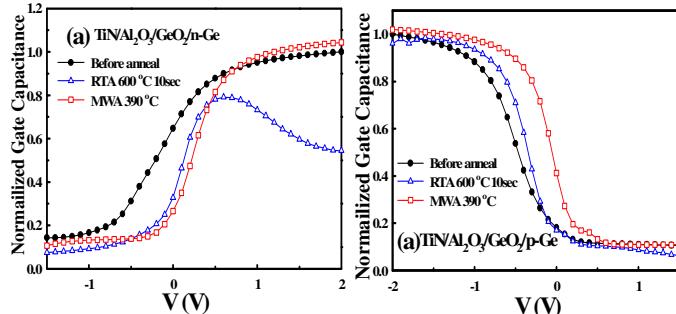

**Gate Dielectric/Channel Interface.** The TiN/Al<sub>2</sub>O<sub>3</sub>/GeO<sub>2</sub> structure of the n- and p-MOS capacitors for C-V characterizations were fabricated on (100) bulk Ge. After interfacial layer formation, Al<sub>2</sub>O<sub>3</sub> was deposited by ALD. From Figs. 4 and 5, an increase of C<sub>ox</sub> and a decrease of the interfacial trap density after MWA were observed. The gate capacitance increases after MWA, which is due to less Ge out-diffusion during low temperature MWA than RTA. The

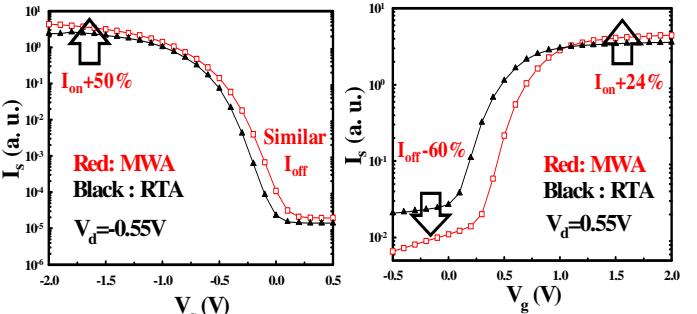

device on/off characteristics are in Figs. 6 and 7. Compared to RTA, MWA produces 50% and 24% drive current enhancements for p- and n-MOSFET, respectively. Their off leakage currents are similar to those by RTA processing.

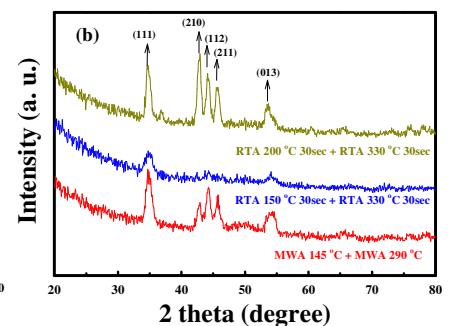

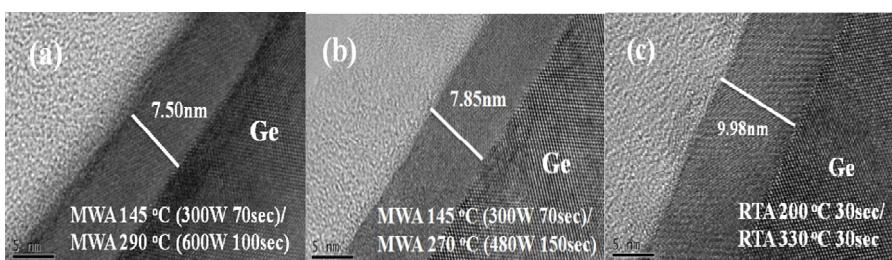

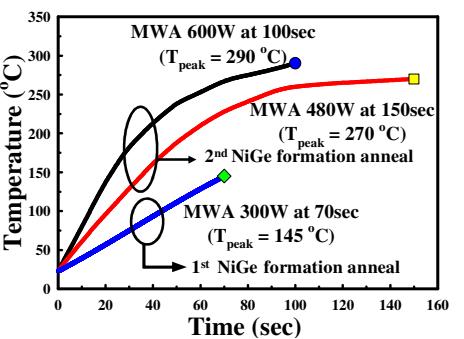

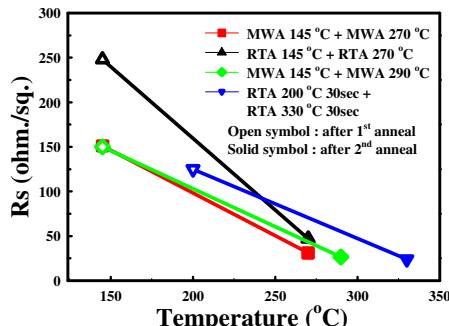

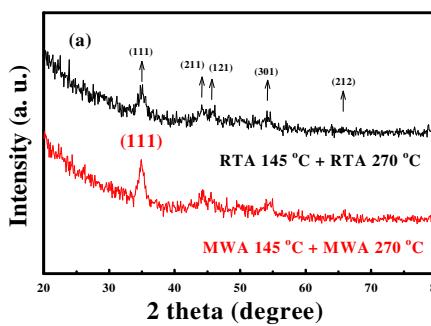

**Ultrathin 7.5nm Ni Mono-Germanide.** In Fig. 8(a), a 7.5 nm NiGe is produced by MWA which meets the target of year 2022 in the ITRS roadmap[6]. The NiGe layer is fabricated on (100) epi-Ge on Si. Unreacted metal was removed after the 1<sup>st</sup> anneal. Afterward, the 2<sup>nd</sup> anneal was performed. The TEM images show an ultrathin NiGe layer with a smooth interface fabricated by MWA at two different microwave power levels during the 2<sup>nd</sup> anneal. Fig. 8(c) shows the result of RTA germanide anneal. The NiGe thickness by RTA is about 2 nm thicker than by MWA. The temperature ramp up curves of MWA for NiGe formation are shown in Fig. 9. The temperature ramped at 2 to 6 °C/sec depending on the microwave power. In Fig. 10, Rs of Ni-Ge by two-step MWA or RTA are summarized. Lower Rs could be obtained by increasing the MWA power with shortened process time, which lowers the peak temperature by 40 °C compared to RTA. In Fig. 11(a), the XRD spectrum for the anneal condition of MWA 145 °C + MWA 270 °C shows strong (111) preferred crystal orientation. In Fig 11(b), an increasing power with shortened process time of 2<sup>nd</sup> step annealing leads to a larger crystallite size. In addition, by lowering the 1<sup>st</sup> step annealing temperature of RTA for reducing the thickness of NiGe, a low intensity of RTA 150 °C + RTA 330 °C shows that it is hard to achieve both the well-defined crystalline structure and the scaling of the NiGe layer. However, the MWA results show that a thinner and lower Rs of NiGe layer was obtained because of the increased crystallinity at low temperature.

### Conclusion

For the first time, Ge MOSFETs with all thermal processes performed by microwave has been realized. Diffusion-less junctions were achieved in Ge was induced by MWA. Compared to the conventional RTA, all MWA processing yields 24% and 50% drive current enhancements for n- and p-MOSFET, respectively due to increased of C<sub>ox</sub> and better gate dielectric/Ge interface. Finally, a record ultrathin 7.5 nm nickel mono-germanide thickness is achieved by two-step low temperature MWA process.

### References:

- [1] G.-L. Luo et al., IEDM Tech. Dig., p. 689, 2009.

- [2] J. H. Park et al., IEDM Tech. Dig., p. 389, 2008.

- [3] S. Y. Lim et al., Appl. Phys. Lett. 97, 182104, 2010.

- [4] K. Martens et al., IEDM Tech. Dig., p.429, 2010.

- [5] J. H. Booske et al., J. Mater. Res., Vol. 7, p. 495, 1991.

- [6] ITRS Roadmap 2011.

**Fig. 1** Schematic diagram of low-temperature microwave annealing (MWA) processed Ge MOSFETs.

**Fig. 2** SIMS and SRP profiles of (a) P and (b)  $\text{BF}_2$  at  $1 \times 10^{15} \text{ cm}^{-2}$  in (100) Ge. The P distribution after MWA is identical to as-implanted, but not after RTA. All boron distribution profiles are close to as-implanted. The insets show the activated levels of P and B by SRP are  $2 \times 10^{19} \text{ cm}^{-3}$  and  $7.5 \times 10^{19} \text{ cm}^{-3}$ .

**Fig. 3** The comparisons of the  $R_s$  between MWA and RTA in (100) Ge. The deep junction of P formed by RTA results in the lower  $R_s$ .

**Fig. 4** p-MOS CV characterizations.  $D_{it}$  and EOT are improved with MWA dopant activation process. RTA process degrads the CV and increases the gate leakage.

**Fig. 5** n-MOS CV characterizations. MWA produced higher gate capacitance and much less gate leakage than RTA.

**Fig. 6**  $I_s$ - $V_g$  of Ge p-MOSFET at  $V_d = -0.55V$ . A 50% drive current enhancement was achieved.

**Fig. 7**  $I_s$ - $V_g$  of Ge n-MOSFET at  $V_d = 0.55V$ . A 24% drive current enhancement and lower leakage current are achieved.

**Fig. 8** HR-TEM images of NiGe by two-step MWA process (a) and (b) using lower power in the 2<sup>nd</sup> step than (a) and by two-step RTA (c).

**Fig. 9** The temperature profiles of MWA for NiGe formation.

**Fig. 10**  $R_s$  of Ni germanide after 1<sup>st</sup> anneal (open symbol) and after 2<sup>nd</sup> anneal (solid symbol).

**Fig. 11** XRD 2 $\theta$ -scan of nickel germanide formed by MWA or RTA. MWA 145 °C + MWA 270 °C produces the relatively strong (111) preferred crystal orientation with low anneal temperature.